Передача информации по каналу с решающей обратной связью

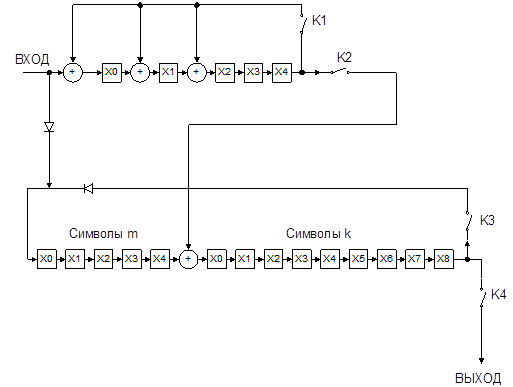

Рис. 2.2. Сруктурная схема декодирования циклического кода с исправлением одной ошибки.

В такте 6 единица с Х4 поступает на сумматоры по модулю 2, и в X0 записывается единица, нуль, находившийся в X0, сложившийся с единицей даст 1 и она запишется в X1 , единица из X1 сложившись с 1 даст нуль и этот нуль запишется в X2, н

уль из X2 перейдёт в X3, а единица из X3 в X4. Далее аналогично.

Таблица 2.2. Работа делителя

|

Номер такта |

Делимое |

Состояние ячеек делителя |

Вес остатка | ||||

|

X0 |

X1 |

X2 |

X3 |

X4 | |||

|

6 7 8 9 10 11 12 13 14 15 16 17 18 |

0 0 0 0 1 0 0 1 1 |

1 0 0 0 0 1 0 0 1 1 0 1 1 |

1 1 0 0 1 1 1 1 0 0 1 1 0 |

0 1 1 0 1 0 1 0 1 1 0 0 0 |

0 0 1 1 0 1 0 1 0 1 1 0 0 |

0 0 0 1 1 0 1 0 1 0 1 1 0 |

3 3 3 3 1 |

В такте 14 синдром (остаток от деления) оказывается записанным в ячейках регистра (10101). Однако его вес W=3 больше числа исправляемых ошибок s, поэтому делитель делает еще один шаг (такт 15), в процессе которого снова осуществляется деление на многочлен Р(Х). Синдром 10110 опять имеет вес W=3. Только после 18 такта W=1=s. В этот момент ключ К1 размыкается, а ключ К2 замыкается и синдром с делителя начинает поступать на сумматор запоминающего устройства, у которого ключ К3 замкнут, а ключ К4 разомкнут.

Это устройство в такте 14 первого этапа полностью заполнилось, а на втором этапе его работы начался циклический сдвиг записанной информации (таблица 2.3). Так в такте 1 единица из ячейки X8 информационных символов переместилась в ячейку X0 контрольных символов m. В такте 2 эта единица передвинулась в ячейку X1, а ее место в ячейке занял следующий нуль и т. д.

Таблица 2.3. Работа ЗУ декодера

|

Номер такта |

Символы m |

Символы k | ||||||||||||

|

X0 |

X1 |

X2 |

X3 |

X4 |

X0 |

X1 |

X2 |

X3 |

X4 |

X5 |

X6 |

X7 |

X8 | |

|

14 1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

1 1 0 0 1 0 0 0 0 0 1 0 0 1 1 |

1 1 1 0 0 1 0 0 0 0 0 1 0 0 1 |

0 1 1 1 0 0 1 0 0 0 0 0 1 0 0 |

0 0 1 1 1 0 0 1 0 0 0 0 0 1 0 |

1 0 0 1 1 1 0 0 1 0 0 0 0 0 1 |

0 1 0 0 1 1 1 0 0 0 0 0 0 0 0 |

0 0 1 0 0 1 1 1 0 0 0 0 0 0 0 |

0 0 0 1 0 0 1 1 1 0 0 0 0 0 0 |

0 0 0 0 1 0 0 1 1 1 0 0 0 0 0 |

0 0 0 0 0 1 0 0 1 1 1 0 0 0 0 |

1 0 0 0 0 0 1 0 0 1 1 1 0 0 0 |

0 1 0 0 0 0 0 1 0 0 1 1 1 0 0 |

0 0 1 0 0 0 0 0 1 0 0 1 1 1 0 |

1 0 0 1 0 0 0 0 0 1 0 0 1 1 1 |

Первые четыре нуля синдрома, поступающие на сумматор, не влияют на работу запоминающего устройства. Лишь в такте 9 единица синдрома, складываясь по модулю 2 с ошибочной единицей символов k (обозначена подчеркиванием), «уничтожают» её, т. е. исправляют ошибку. Регистр запоминающего устройства продолжает переключаться до окончания второго цикла (этапа) его работы. После такта 14 ключи К2 и К3 размыкаются, а ключи К1 и К4 замыкаются: начинается считывание исправленной комбинации и одновременная запись новой.

Таким образом, декодирование состоит их двух этапов. На первом этапе осуществляются нахождение остатка и запись кодовой комбинации, на втором — ее исправление и расстановка символов k и m на свои места.

2.3 Модульная структура решателя кодера и его работа

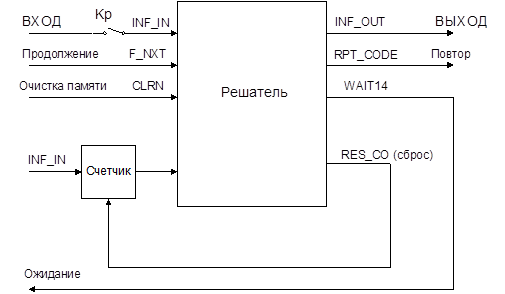

Решатель кодера должен выполнять следующие задачи: обеспечить связь с передающим устройством, передачу сигналов задержек при исправлении ошибок и повторных передачах информации. Также должен выполнять свою основную функцию – приём сигнала продолжения. Структурная схема решателя приведена на рисунке 2.3.

Рис. 2.3. Сруктурная схема решателя кодера.

Рассмотрим все случаи более подробно.

1. Сообщение проходит без ошибок. Решатель принимает сигнал продолжения (F_NXT). Ключ Кр открывается и начинает поступать следующее сообщение. Так как длина сообщения составляет 9 символов, то в конце такта 9 ключ Кр размыкается, и на передающее устройство поступает сигнал ожидания посылки сообщения (WAIT14). Далее решатель начинает ожидать сигнал продолжения.

2. Сообщение прошло с ошибкой. Пусть искажение произошло только в одном символе. Тогда решатель на 14 такте не получает сигнал продолжения. Ключ Кр размыкается. Решатель посылает сигнал ожидания на передатчик в течение 14 тактов (этап 2). За это время искаженная комбинация исправляется, и с решателя декодера приходит сигнал продолжения, Кр замыкается.

3. Сообщение содержит более одной ошибки. Всё происходит аналогично пункту 2, за исключением того, что и после 14 такта второго этапа ожидания он не получает сигнал продолжения и ключ Кр остается разомкнутым. Тогда ещё в течение 14 тактов (этап 3) решатель посылает на передатчик сигнал ожидания (WAIT14), но на кодер посылается сигнал повтора сообщения из буфера (RPT_CODE).

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем