Передача информации по каналу с решающей обратной связью

Когда входы одинаковы, на выходе 0, если разные, то 1.

X1X2Y

000

011

101

110

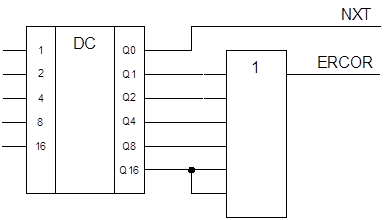

7. Решатель декодера.

Представляет собой обыкновенный двоично-десятичный дешифратор на 5 входов – 32 выхода и шестивходовой элемент ИЛИ.

На вход подается остаток от деления. Если он равен 0, то активизируется выход Q0 (это соответствует сигналу NXT – ошибок нет), если вес остатка равен 1

, то активны Q1, Q2, Q4, Q8, Q16 (это соответствует сигналу ERCOR – ошибка исправима).

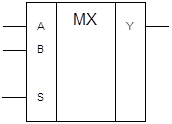

8. Мультиплексор на два канала.

Выполняет роль коммутатора каналов. Используется как в кодере, так и в декодере.

Входы |Выход

S A B |Y

0 х 1 |1

0 х 0 |0

1 1 х |1

1 0 х |0

2.6 Описание функциональной схемы кодера и решателя кодера

Работа кодера и решателя кодера была описана выше. Поясним некоторые моменты.

При начале передачи передатчик начинает посылать новый пакет сообщений. Сначала посылается сигнал очистки памяти кодера и решателя (CLRN = 0). Затем он становится равен 1.

Далее начинает передаваться сообщение № 1 на вход решателя кодера (INF_IN), состоящее из 9 символов. Оно поступает на ключ Кр, который выполнен на элементах DD1.21 и DD1.22. Одновременно оно поступает и на кодер через ключ К2, реализованный на элементах DD2.13 и DD2.14.

В кодере предусмотрен буфер на 14 бит, в который записывается закодированное сообщение. Это позволит на аппаратном уровне осуществлять повтор сообщения, не «отвлекая» передатчик, в роли которого выступает ЭВМ. Это позволит при ошибках, не прерывать другие задачи, которые могут выполняться на данной ЭВМ и использовать её только в качестве источника информации, не нагружая дополнительными задачами. Можно было его сделать и на 9 бит, но емкость примененной микросхемы позволяет применить и 14 битный буфер. Буфер управляется ключами, которые выполняют необходимые коммутации, соединение с кодером, запись уже закодированного сообщения и т.п. Ключи реализованы на элементах DD2.4, DD2.3, DD2.2, DD2.34 и DD2.35. Элементы памяти выполнены на триггерах D-типа (элементы DD2.20 – DD2.33).

Отсчет количества бит сообщения производится с помощью счетчиков: DD1.9, DD1.17 – в решателе кодера и DD2.16 – в кодере.

Делитель предназначен для получения контрольных символов. Его работа была рассмотрена выше. Он выполнен на элементах DD2.5 – DD2.12.

Дешифратор и другие логические элементы используются для работы ключей и включения/выключения каналов передачи.

2.7 Описание функциональной схемы декодера и решателя декодера

Работа декодера и решателя декодера была описана выше. Поясним некоторые моменты.

При приеме первого сообщения пакета посылается сигнал очистки памяти кодера и решателя (CLRN = 0). Затем он становится равен 1.

Далее начинает приниматься сообщение № 1 на вход делителя и в память декодера (INFA), состоящее из 14 бит. Оно поступает на сумматор по модулю 2, который выполнен на элементе DD1.1 и соответственно оно поступает и в ОЗУ декодера. Память предназначена для хранения полученного сообщения.

Отсчет количества бит сообщения производится с помощью счетчиков: DD1.16, DD1.23.

Делитель предназначен для получения остатка от деления. С выходов делителя на дешифратор DD1.12 поступает остаток, соответственно при остатке с весом 0 посылается сигнал продолжения (NXT). Если вес остатка равен 1, то посылается сигнал ERCOR (ошибка исправима). Делитель выполнен на элементах DD1.1 – DD1.8.

Дешифратор (DD1.32) и другие логические элементы используются для работы ключей и включения/выключения каналов передачи.

2.8 Описание принципиальной схемы кодера и решателя кодера

Полученные кодер и решатель представляет собой микросхемы, с функциями, которые были описаны в функциональной схеме.

В итоге имеем две микросхемы, одна из них выполняет функции решателя, а другая функции кодера.

У решателя имеются следующие входы:

INF_IN – информационный;

CLRN – очистка памяти решателя;

CLK – вход генератора тактовых импульсов;

F_NXT – принимает сигнал о продолжении;

И имеются следующие выходы:

INF_OUT – информационный выход;

RPT_CODE – сигнал повтора;

WAIT14 – сигнал приостановки посыла информации с передатчика;

Далее идут выходы, которые несут чисто информационный характер для показа внутренней работы микросхемы и непосредственно не используются:

RES_CO – сигнал сброса счетчиков;

CN1…CN5 – разряды счетчика решателя;

Далее рассмотрим кодер.

Входы:

RPT – прием сигнала RPT_CODE;

CLRN – очистка памяти кодера;

CLK – вход генератора тактовых импульсов;

INFA – информационный вход;

Выход один, это OUT – посыл закодированного сообщения либо в линию связи (ЛС), либо на модулятор (в зависимости от вида устройства: если ЛС аналоговая, то на модулятор, если цифровая, то непосредственно в ЛС).

Также имеется разъем для соединения с ЛС и передающим устройством, а также для подвода питания.

Опишем работу полученного устройства.

Решатель.

Пусть с передатчика пришло сообщение 011001010. Сигнал F_NXT=0. Всё это время сигнал очитки памяти выключен (CLRN = 1). На такте 9, счетчик досчитает до 8 (01000), так как он начинает считать с нуля. За эти девять тактов всё полученное сообщение поступает на выход INF_OUT. После девятого такта включается сигнал WAIT14, потому что необходимо ещё закодировать сообщение.

Кодер кодирует сообщение, и посылает в течение 5 тактов пять контрольных символов. Допустим в декодер сообщение поступило с ошибкой. Сигнал F_NXT не пришел, то есть F_NXT=0 в течение всех 14 тактов. Тогда счетчик считает далее до 27 (11011), и всё это время на передатчик поступает сигнал приостанова посылки сообщения, так как идёт попытка исправления искаженного сообщения в декодере.

Пусть в декодере сообщение не исправилось, тогда сигнал F_NXT не приходит, то есть опять F_NXT=0. И соответственно после 9 такта на информационный выход ничего не поступает. Не получив на 28 такте сигнала F_NXT решатель сбрасывает счетчик решателя RES_CO=1, и послав на передатчик сигнал приостанова, отправляет на кодер сигнал повтора RPT_CODE = 1.

С буфера кодера в течение 14 тактов сообщение заново посылается в ЛС.

Пусть теперь сообщение в декодере было принято без ошибок. На 14 такте приходит сигнал F_NXT, решатель снова сбрасывает счетчик и принимает новое сообщение с передающего устройства, предварительно сбросив сигнал WAIT14 в нуль.

Соответственно далее всё происходит подобным образом. Более подробно работа решателя приведена в приложении на временной диаграмме.

Кодер.

Пусть с решателя кодера пришло сообщение 011001010. Сигнал повтора сообщения RPT_CODE=0. Всё это время сигнал очитки памяти выключен (CLRN = 1).

Кодер в начале первые 9 тактов просто выводит сообщение на выход. Одновременно оно записывается в память кодера. Затем посылает в течение 5 тактов пять контрольных символов. Допустим с решателя кодера поступает сигнал повтора посылки сообщения RPT_CODE=1. Тогда в течение 14 тактов кодер уже из памяти отсылает в ЛС (вывод OUT) сообщение заново.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем