Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

Список условных сокращений

АЛМ – алгебро-логический метод

АЛУ – арифметико-логическое устройство

ВЭП – вектора экспериментальной проверки

ГАС – гибкая автоматизированная система

ДНФ – дизъюнктивная нормальная форма

КНФ – конъюнктивная нормальная форма

ТН – таблица неисправностей

ATPG – Automated Test Pattern Generator

BIRA – Built-In Repair Analysis

BIS

R – Built-In Self Repair

BIST – Built-In Self Test

ESL – Electronic System Level

FDT – Fault Detection Table

F-IP – Functional Intellectual Propert

IEEE – Institute of Electrical and Electronics Engineers

I-IP – Infrastructure Intellectual Property

SoC – System-on-Chip

TLM – Transaction Level Modeling

Содержание

Введение

1. Анализ технического задания

1.1 Состояние рынка технологий сервисного обслуживания SoC

1.2 Структура сервисов SoC-микросхем

1.2.1 Модуль синтеза тестов

1.2.2 Модуль анализа неисправностей

2. Алгоритмическое и программное обеспечение тестирования пакета кристаллов ГАС

2.1 Алгебро-логический метод диагностирования неисправностей

2.2 Алгоритмизация АЛМ диагностирования неисправностей

2.3 Алгебро-логическая модель диагностирования F-IP

2.4 Уточнение диагноза F-IP, с помощью моделирования

2.5 Условное диагностирование F-IP на основе ДНФ

2.6 АЛМ для тестирования и ремонта SoC-памяти ГАС

2.7 Формализация АЛМ ремонта памяти

Выводы

Перечень ссылок

Введение

Вычислительная и аппаратная сложность современных гибких автоматизированных систем (ГАС), в основу организации которых заложены цифровые системы на кристаллах (System-on-Chip – SoC), характеризующиеся миллионами эквивалентных вентилей и требующих создания и внедрения новых высокоуровневых технологий проектирования – Electronic System Level (ESL) Design, моделинга – Transaction Level Modeling (TLM) и встроенного сервисного обслуживания – Infrastructure Intellectual Property (I-IP). Это означает, что поиск быстродействующих методов и средств приводит всех исследователей к необходимости повышения уровня абстракции моделей создаваемых функциональностей – Functional Intellectual Property (F-IP), встраиваемых в кристалл [1].

Рынок программных продуктов EDA уже предлагает инструменты для автоматизации процессов моделинга и верификации устройств системного уровня, начиная с компиляторов HDL-языков (C++, SystemC, SystemVerilog, UML, SDL) [2] и заканчивая графическими оболочками (Simulink, LabView, Xilinx EDK). Данные средства позволяют создавать проекты из существующих библиотечных компонентов путем использования ESL-мэппинга и создания TLM-интерфейсов [3, 4].

Рыночная привлекательность имплементации цифровой системы в кристалл FPGA определяется применением сравнительно дешевых чипов вместо универсальных процессоров, малой потребляемой мощностью, габаритными размерами, качественным и надежным выполнением основных функций, благодаря встроенной I-IP-инфраструктуре, что является актуальным в век мобильных вычислительных устройств.

Цель исследования – разработать алгоритмическое и программное обеспечение для тестирования пакета кристаллов ГАС, в соответствии со стандартом IEEE 1500.

Объект исследования – пакет кристаллов ГАС.

1. Анализ технического задания

1.1 Состояние рынка технологий сервисного обслуживания SoC

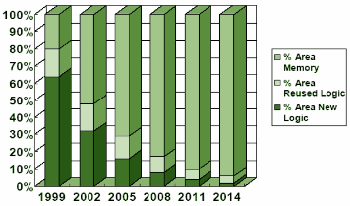

Проблема диагностирования и ремонта памяти связана с тенденцией на постоянное уменьшение площади кристалла, отводимой для оригинальной и стандартизованной логики с одновременным увеличением встроенной памяти. Как показано на рис. 1.1, увеличение удельного веса памяти на кристалле приводит к ее полному доминированию для хранения данных и программ, которое к 2014 году достигнет 94% [5]. Это обеспечит не только высокое быстродействие выполнения функциональности, но и гибкость, свойственную программному продукту в части коррекции ошибок проектирования.

Рисунок 1.1 – Удельный вес SoC-памяти

Особенностью элементов памяти является тот факт, что в процессе их изготовления и эксплуатации отдельные ячейки под воздействием неисправностей могут выходить из состояния работоспособности. Данное обстоятельство не всегда приводит матрицу памяти к критическому состоянию, когда восстановление работоспособности невозможно. Поэтому далее рассматривается такое техническое состояние памяти, при котором суммарное количество дефектных ячеек не превышает резервных возможностей изделия, предназначенных для ремонта.

Современные технологии проектирования цифровых систем на кристаллах предлагают, наряду с созданием функциональных блоков F-IP, разработку сервисных модулей I-IP, ориентированных на комплексное решение проблемы качества проекта и повышение выхода годной продукции (Yield) в процессе производства, которое определяется внедрением в кристалл следующих сервисов [6]:

1) Наблюдение за состоянием внутренних и выходных линий в процессе функционирования, верификации и тестирования штатных блоков на основе использования стандарта граничного сканирования IEEE 1500 [7, 8];

2) Тестирование функциональных модулей путем подачи проверяющих наборов от различных тестовых генераторов, ориентированных на проверку дефектов или исправного поведения;

3) Диагностирование отказов и дефектов путем анализа информации, полученной на стадии тестирования и использования специальных методов встроенного поиска неисправностей на основе стандарта IEEE 1500;

4) Восстановление работоспособности функциональных модулей и памяти после фиксации отрицательного результата тестирования и определения места и вида дефекта при выполнении фазы диагностирования;

5) Измерение основных характеристик и параметров функционирования изделия на основе встроенных средств, позволяющих производить временные и вольтамперные измерения;

6) Надежность и отказоустойчивость функционирования изделия в процессе эксплуатации, которая достигается диверсификацией функциональных блоков, их дублированием и восстановлением работоспособности SoC в реальном масштабе времени.

1.2 Структура сервисов SoC-микросхем

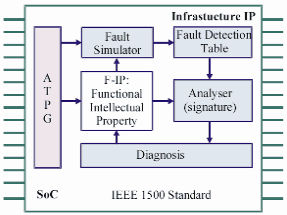

На рис. 1.2 представлена усеченная структура [9, 10, 11], ориентированная на выполнение следующих задач:

1) Тестирование функциональностей на основе генерируемых входных последовательностей (Automated Test Pattern Generator – ATPG) и анализа выходных реакций;

2) Моделирование (Fault Simulator) неисправностей [12] в целях обеспечения диагностирования и ремонта на основе таблицы неисправностей (Fault Detection Table – FDT);

3) Диагностирование дефектов с заданной глубиной, путем использования мультизонда стандарта IEEE 1500;

4) Встроенный ремонт матричной памяти, на основе использования запасных компонентов (spare) [13].

Рисунок 1.2 – Инфраструктура сервисов SoC DSP

1.2.1 Модуль синтеза тестов

Модуль синтеза тестов, предназначен для проверки функциональностей и одиночных неисправностей. В его состав входит набор генераторов входных последовательностей, обеспечивающих создание следующих тестов [14]:

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем