Технология GPRS

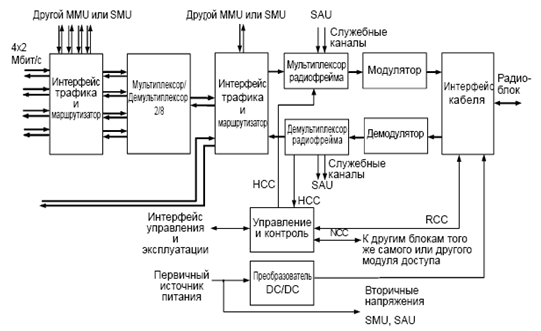

Мультиплексор/демультиплексор 2/8 Мбит/с (только для MMU 4x2/8). Мультиплексирование и демультиплексирование сигнала 4x2 Мбит/с соответствует ITU-T Rec G.703 и G.742. В направлении мультиплексирования четыре основных входных сигнала 2 Мбит/с принимаются и декодируются. При этом извлекаются поступающие синхросигналы, а информация трафика считывается в буферную память. Коэффициент заполнения буфе

рной памяти контролируется положительным выравниванием. Четыре синхронизированных сигнала вместе с указателями выравнивания и битами границ фрейма впоследствии мультиплексируются в сигнал 8 Мбит/с. В направлении демультиплексирования производится разборка фрейма, после определения границ фрейма четыре основные сигнала посылаются в устройство буферной памяти, при этом должны быть удалены показатели выравнивания и избыточные биты. Скорость считывания из буферной памяти контролируется кварцевым генератором; считанный сигнал фильтруется, чтобы уменьшить дрожание фазы (джиттер). В конечном счете, сигнал становится линейно-кодированным и переданным.

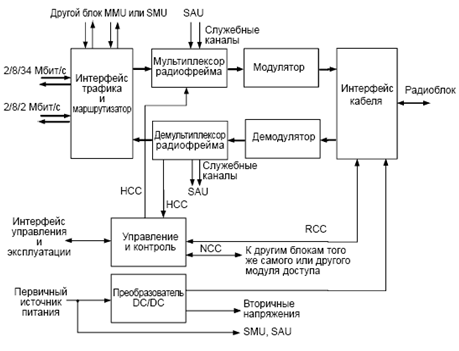

Рисунок 2.12 – Блок-схема для конфигураций 2x2, 2x8 и 34+2 Мбит/с

Мультиплексор радиофрейма и Упреждающая Коррекция Ошибок (FEC). Три различных типа данных мультиплексируются в поток данных, передаваемых по каналу радиосвязи:

- трафик;

- данные служебного канала;

- данные служебного канала пролета (HCC).

Передача данных трафика. Передающиеся данные трафика сначала поступают в мультиплексор, чтобы обеспечить принятый темп передачи данных (заполнение канала). Если на входе нет корректных данных, то включается подача сигнала AIS, передаваемого с номинальной скоростью. Это означает, что трафик данных через пролет заменен единицами.

Рисунок 2.13 – Блок-схема для конфигурации 4x2/8 Мбит/с

Передача данных служебного канала. Предусмотрены два независимых служебных канала. Аналоговые и цифровые служебные данные обрабатываются по-разному. SAU получает тактовые и синхронизирующие импульсы и данные из SAU подаются в мультиплексор. Цифровые данные и синхроимпульсы байтов вначале подаются в несинхронный буфер, а затем считываются в синхронном режиме, определяемом тактовой частотой. При этом формируются сигналы заполненности, обеспечивающие нормировку различимости данных.

Служебный канал пролета (HCC) используется для обмена управляющей и обслуживающей информацией между MMU на ближнем и дальнем концах пролета.

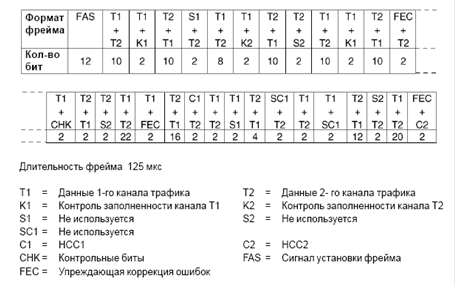

Три разных типа данных вместе с контрольными и ограничивающими фрейм битами передаются в составном формате данных, который определяется содержанием специального ОЗУ, содержащего параметры, определяющие формат фрейма. В начале фрейма помещаются 12 сигнальных битов. В составной фрейм включаются также биты, несущие информацию о его заполненности.

Шифровка и кодировка упреждающей коррекции ошибок (FEC). Синхронный шифровщик имеет объем 217-1 бит и синхронизируется каждым восьмым фреймом (суперфреймом). Биты FEC вычисляются с использованием схемы перестановок и включаются в позиции, которые определяются форматом фрейма.

Составной поток данных представляется фреймом длительностью 125 мкс, который включает все описанные выше типы данных.

В соответствии с рисунком 2.14 показана структура канала радиофрейма для 2x2 Мбит/с.

Используются следующие скорости передачи составного потока битовых данных:

- 4.5195 Мбит/с для канала 2x2 Мбит/с;

- 8.9316 Мбит/с для канала 4x2/8 Мбит/с;

- 17.6071 Мбит/с для канала 2x8 Мбит/с;

- 37.5369 Мбит/с для канала 34+2 Мбит/с.

Поставляется три различные версии SMU (SMU Sw, SMU 8x2 и SMU 16x2) для различных скоростей трафика.

Модулятор. Составной поток данных, обработанных мультиплексором радиофрейма, далее модулируется с использованием C-QPSK*. Импульс преобразуется из постоянного тока в переменный, после чего, с помощью фильтра Найквиста, импульсу придается форма, обеспечивающая оптимальный спектр передаваемого сигнала.

Модулятор содержит управляемый напряжением генератор (voltage controlled oscillator, VCO), генерирующий сигнал с частотой 350 МГц. Он смешивается с сигналом частотой 490 МГц, выделенный сигнал с частотой 140 МГц используется для целей контроля.

Демультиплексор радиофрейма и упреждающая коррекция ошибок (FEC). На получающей секторной поступающий составной поток данных демультиплексируется и FEC корректируется. Функция выравнивания фрейма ищет образцы битов выравнивания фрейма, которые есть в получаемом потоке данных и, соответственно, подстраивает приемник.

FEC выполняется с использованием битов четности FEC и результатов измерения качества передачи данных, поступающих от демодулятора. Дешифратор псевдослучайных последовательностей восстанавливает первоначальное состояние сигнала, позволяющее демультиплексору правильно распределять полученную информацию по соответствующим каналам.

Демультиплексирование выполняется согласно хранящемуся в памяти формату фрейма. Демультиплексор генерирует сигнал сбоя фрейма в том случае, если нарушена его синхронизация. Число ошибочных битов в потоке данных трафика измеряется с использованием битов четности. Они используются для определения уровня битовых ошибок (BER) и проверки качества функционирования. Биты контроля заполненности обрабатываются для каналов трафика и служебных каналов.

Рисунок 2.14 – Пример структуры фрейма канала радиосвязи для 2x2 Мбит/с

На принимающей сектороне выполняются следующие процедуры для данных трафика:

- введение AIS (при потере сигнала или BER < 10-3);

- обнаружение AIS;

- гибкая буферизация и восстановление тактовых импульсов;

- измерение выровненности потоков данных и их согласование, необходимые для того, чтобы обеспечить переключение без сбоев в сигнале трафика (hitless switching);

- переключение без сбоев в сигнале трафика (в защищенных системах 1+1).

Для цифрового канала извлекаются данные и синхросигналы и, с использованием несинхронного буфера, восстанавливается тактовая частота. В аналоговом канале сигналы синхронизации и тактовые сигналы подаются вместе с сигналами данных.

Демодулятор. Полученный 140 МГц сигнал усиливается с использованием системы АРУ и фильтруется до преобразования в исходный I/Q сигнал. Затем этот сигнал пропускается через фильтр Найквиста с целью восстановления формы импульсов, детектируется и C-QPSK демодулируется.

Управление и контроль. Микропроцессорная система управления и контроля (CSS) встроена во все блоки модуля доступа. Ее основным назначением является сбор сигналов о неисправностях, управление установками и контроль. Неисправности индицируются светодиодами, расположенными на лицевых панелях блоков.

Процессор MMU обменивается данными с другими процессорами в модуле доступа по каналу NCC. Обмен данными управления и контроля в пролете производится по каналу HCC. Процессор также связан с ПК через интерфейс Управления и Эксплуатации.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

- Анализ задачи общего воздействия динамическим магнитным полем на человека и формирование требований на технические средства комплексной магнитотерапии

- Индивидуальный прием программ спутникового вещания

- Методология организации климатических испытаний РЭА. Испытания на воздействие тепла и холода

- Тяговый генератор переменного тока ГС501АУ1

- Коммуникаторы, их свойства и функции

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем