Проектирование вычислительного устройства

![]()

|

|

| ||||

|

|

1 |

1 |

| ||

|

1 |

D |

1 |

| ||

|

|

1 | ||||

|

1 |

1 |

| |||

|

|

|

| |||

![]()

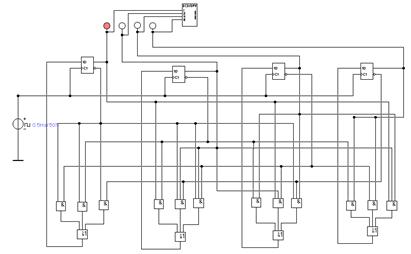

Построим схему в среде Electronics Workbench (рис. 4):

Рис. 4

4. Синтезирование вычислительного устройства для реализации алгоритма вычислений на дискретных элементах (Если A > B, то Y = A * C + B иначе Y = A + B * C)

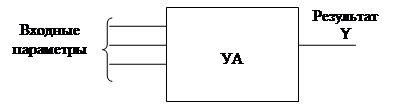

Согласно заданию, нам нужно спроектировать управляющий автомат, который будет реагировать на изменение входных параметров на входе, изменением результата на выходе, т.е. с обратной связью и является асинхронным. Управляющий автомат должен обладать большим быстродействием. Это достигается использованием матричных умножителей.

Структурная схема УА представлена на рисунке 5.

|

Рис.5

Структурная схема функционирования УА представлена на рисунке 6

|

Рис.6

Алгоритм работы:

Определение начальных условий (значений A,B,C)

Значение С поступает на 1-ый вход блока умножения.

Значения А и В поступают на входы блока сравнения.

Результатом работы блока сравнения являются значения MIN и MAX.

MAX поступает на второй вход блока умножения.

MIN поступает на первый вход блока суммирования.

Результат из блока умножения поступает на второй вход блока суммирования. Получение результата из блока суммирования, т.е. значения Y. Для сравнения чисел используется компаратор, который будет реализован на логических элементах.

Компараторы

Компаратор – функциональный узел для определения отношения между двумя двоичными числами.

Основными отношениями являются “=” (FA=B), “>” (FA>B), остальные отношения получаются из основных:

![]() ,

, ![]() ,

, ![]()

равнение на равенство осуществляется путем поразрядного сравнения двух чисел.

|

ai |

bi |

ri |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

1 |

ri – признак равенства bi разряда

Признак равенства одноразрядных чисел можно записать как

![]()

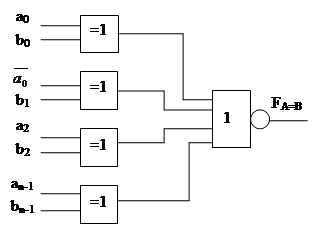

Многоразрядный компаратор на равенство состоит из элементов ИСКЛ. ИЛИ для поразрядного сравнения (рисунок 7).

|

A = an-1 an-2 … a1 a0

B = bn-1 bn-2 … b1 b0

Рис.7

Сравнение на “больше” “>” не является поразрядной операцией. Составим таблицу истинности для сравнения на “>” одноразрядных чисел:

|

A |

B |

FA>B |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

![]()

Функцию для 2-х разрядных чисел определим так, если в старшем разряде А = 1 и В = 0, то FA>B = 1 независимо от содержания младших разрядов; если старшие разряды одинаковы, то надо перейти к сравнению младших разрядов, рассуждая далее аналогично. Таким образом, для 2-х разрядных чисел: ![]() , где r1 – признак равенства старших разрядов a1 и b1.

, где r1 – признак равенства старших разрядов a1 и b1.

Распространяя рассуждения на многоразрядные числа, получим

![]()

В этом выражении ri – признаки равенства чисел в i-разрядах.

Микросхема компаратора обычно имеет дополнительные входы с теми же обозначениями, что и выходы A = B, A > B, A < B, которые используются для наращивания компаратора путем каскадного соединения схемы.

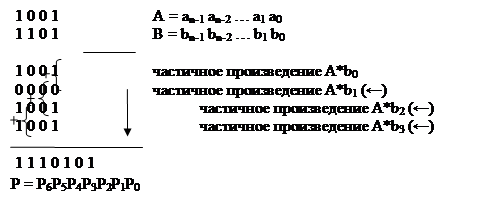

Умножение чисел

Процедура ручного умножения множимого A = an-1 an-2 … a1 a0 на множитель B = bn-1 bn-2 … b1 b0 заключатся в образовании частных произведений множимого A на разряды множителя B, при этом частичные произведения располагаются в разрядной сетке всякий раз со сдвигом на 1 разряд влево. Далее частичные произведения складываются для получения произведения P = P2n-1 …P1 P0. Результатом умножения множимого на разряд множителя bi равен 0 в случае bi = 0 или самому множимому A в случае, когда bi = 1, следовательно, для умножения A×bi можно использовать блок конъюнкторов (рисунок 8):

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем