Проектирование вычислительного устройства

|

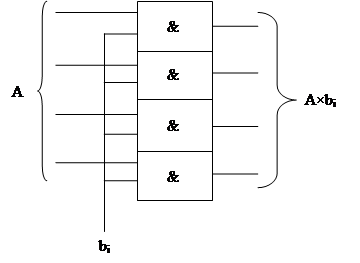

Рис.8

Наиболее высокое быстродействие достигается в матричных умножителях, в которых все частичные произведения образуются одновременно на разных блоках конъюнкторов, совмещены

во времени, но разделены в пространстве, произведение сразу же образуется с помощью набора из (n-1) сумматоров (n – разрядность чисел), причем сдвиг в разрядной сетке частичных произведений выполняется монтажным способом. Составим блок-схему алгоритма работы УА.

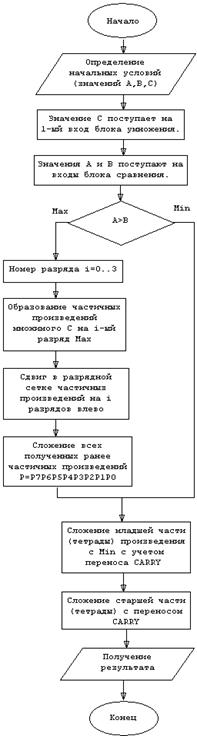

Схема работы вычислительного устройства (рисунок 9)

Рис.9

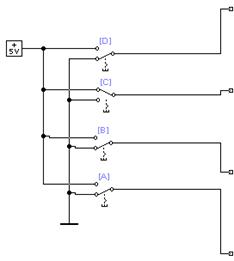

Данные А, В и С будут определяться с помощью блока переключателей, реализуемого следующей схемой (рисунок 10):

Рис.10

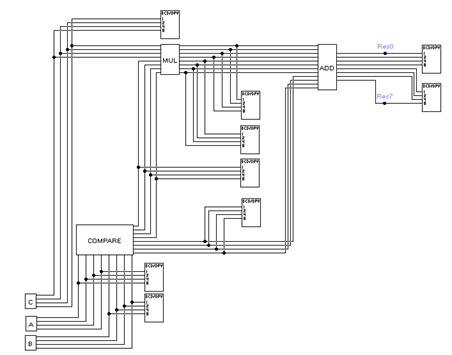

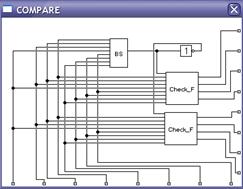

Анализ А и В происходит в Блоке сравнения (COMPARE) (рисунок 11):

Рис.11

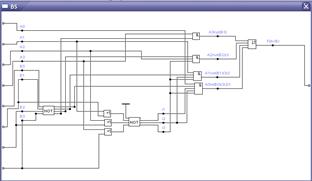

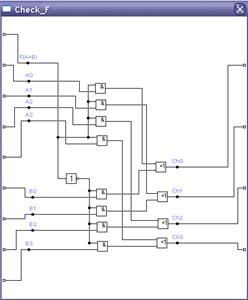

В соответствии с сигналом компаратора BS (рисунок 12) подается сигнал на блоки Check_F (рисунок 13)

Рис.12

Рис.13

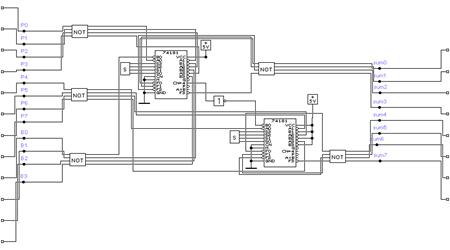

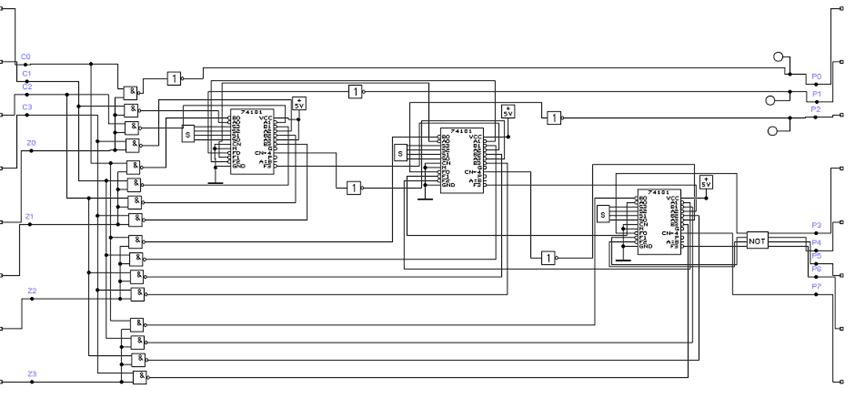

В результате Max подается в Блок умножения (MUL) (рисунок 14), а Min в Блок сложения (ADD) (рисунок 15)

Блок сложения (ADD):

Рис.15

Блок умножения (MUL):

Рис.14

Вывод

Достоинства данного метода очевидны, так как при его реализации выполняется критерий минимума аппаратных затрат и максимум быстродействия по сравнению с методом, в котором умножение двух чисел заменятся сложением.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

- Разработка печатного модуля РЭС с использованием учебных алгоритмов САПР

- Общая характеристика систем контроля и управления доступом

- Виды индукторов и создаваемых ими полей

- Разработка приёмного полукомплекта телеуправления

- Разработка функциональной цифровой ячейки от функциональной логической схемы проектируемого узла до печатной платы узла

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем