Аналоговые перемножители напряжения

Диапазон допустимого синфазного сигнала для различных полярностей сигнала Х:

– для положительной полярности

![]()

– для отрицательной полярности

![]() ,

,

где UИТ – падение напряжения на источнике тока I0, поэтому меньшее по абсолютной величине значение и будет

определять допустимый синфазный диапазон входного напряжения.

Допустимое синфазное напряжение для входа Y также различно для положительной и отрицательной полярности напряжения UY:

– для отрицательной полярности

![]()

– для положительной полярности

![]() .

.

Для обеспечения максимально возможного диапазона линейного изменения выходного напряжения необходимо выполнить условие:

![]()

Легко показать, что при напряжениях питания ±15 В и токе I0 = 0,5 – 2 мА реально обеспечить возможность работать с напряжениями ![]() но при низких напряжениях питания (например, ±5 В) эти напряжения не могут быть больше 1-2 В, а при напряжении питания ±1,5 – всего лишь 50-100 мВ.

но при низких напряжениях питания (например, ±5 В) эти напряжения не могут быть больше 1-2 В, а при напряжении питания ±1,5 – всего лишь 50-100 мВ.

При построении перемножителей напряжения на основе транзисторов, выполненных по технологии SiGe (кремний на германии) [20], имеющих, как правило, очень низкое пробивное напряжение, проблема применения линеаризующих цепей стоит наиболее остро. Очевидно, что применение линеаризации в ПНТ требует увеличения напряжения питания на один-два перехода база-эмиттер, что не всегда допустимо.

При исследовании АП, выполненного на основе транзисторов SGB25 (npnVp) [20] с максимальным напряжением UКЭ< 3 В по схеме АП (рис. 2.2), были получены следующие результаты.

Линейность перемножителя оценивалась следующим образом. На один из входов, например Y, подавалось постоянное напряжение, а на вход X – изменяющееся в заданном диапазоне. Изменяющееся напряжение подается дифференциально, а оценка линейности производится следующим образом:

%,

%,

где UВЫХ – парафазное выходное напряжение перемножителя; UХ – дифференциальное входное напряжение, К – масштабный коэффициент перемножителя.

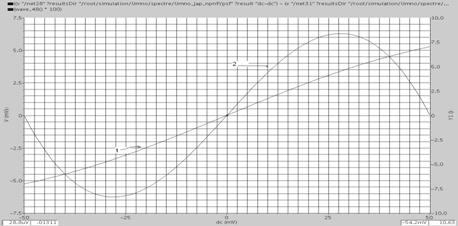

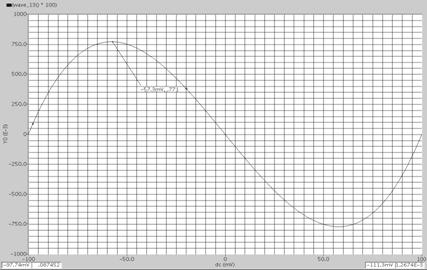

Результаты моделирования (в среде Cadence) при UY = 100 мВ и UX= ± 100 мВ и RН = 50 Ом приведены на рисунке 5.8. Максимальное выходное напряжение составляет 22 мВ, что соответствует масштабному коэффициенту преобразования К = 4,5. Отклонение от линейности составляет ± 0,022 %. Столь высокая линейность объясняется полной симметрией схемы и взаимной компенсацией нелинейности преобразования разности напряжений база-эмиттер и напряжения коллектор-база (напряжение коллектор-база транзисторов при питании от ±1,5 В становится отрицательным при UX > 80 мВ, однако сохраняется активный режим работы транзистора – без насыщения).

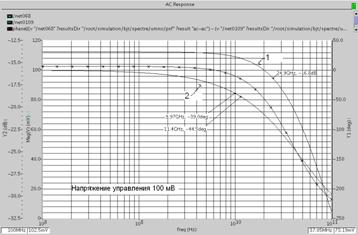

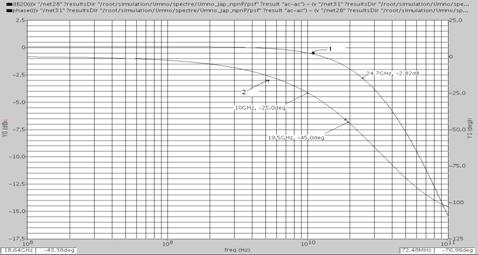

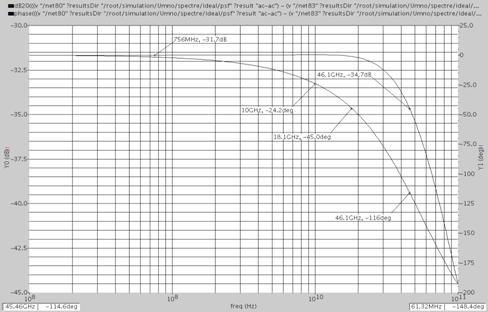

На рисунке 5.9 представлены графики, характеризующие частотные свойства перемножителя. Полоса пропускания перемножителя по уровню –3дБ составляет 25 ГГц (при частоте fT = 80 ГГц).

Как уже отмечалось, проблема построения высоколинейного перемножителя для низковольтных питающих напряжений достаточно сложна. Обычно цепи компенсации, повышающие линейность перемножителя, тем или иным способом измеряют ток в преобразователе «напряжение-ток» и формируют компенсирующее воздействие. В этом случае, как правило, требуется последовательное включение в цепи коллекторов дополнительных диодов, что потребует повышения питающих напряжений [6]. На рисунке 2.9 представлена схема балансного смесителя, способная работать при напряжении питания не более 3UБЭ. Линейность этой схемы можно оценить с помощью выражений (2.1) и (2.3), а крутизну преобразования – с помощью выражений (5.1) и (5.2):

Рис. 5.8. График изменения выходного напряжения перемножителя (кривая 1) и отклонение от линейности в % (кривая 2), выполненного по схеме (рис. 2.2) на транзисторах типа SGB25

Рис. 5.9. АЧХ и ФЧХ перемножителя по схеме (рис. 2.2) на транзисторах типа SGB25

(5.1)

(5.1)

(5.2)

(5.2)

Рис. 5.10. Низковольтный балансный смеситель

Рис. 5.11. График изменения выходного напряжения смесителя (1) и отклонение от линейности в % (2) при входном сигнале 50 мВ

Рис. 5.12. Логарифмические АЧХ (1) и ФЧХ (2) смесителя

Линейность смесителя оценивалась по той же методике, что и линейность перемножителя при уровне входного сигнала 50 мВ. Как и следовало ожидать, нелинейность весьма высока и превышает 6 %.

Логарифмические АЧХ и ФЧХ сняты при управляющем воздействии 175 мВ, при этом частота среза составила 24,7 ГГц при RН = 50 Ом.

Балансный смеситель, схема которого представлена на рисунке 5.10, обладает низким диапазоном входного сигнала при заданной линейности – не более 50 мВ. Проблему линеаризации такого смесителя и, по сути, превращения его в линейный перемножитель можно решить следующим образом. Как и в случае с перемножителем на основе множительного ядра Джильберта линеаризацию передаточной характеристики дифференциального каскада можно осуществить логарифмированием входного сигнала (рис. 5.13). Причем каналы X и Y в этом случае остаются абсолютно симметричны, и длина электрического пути для сигналов UX и UY одинакова.

Рис. 5.13. Схема перемножителя, полученная модифицированием схемы балансного смесителя

Результаты моделирования схемы АП (рис. 5.13) представлены на рисунках 5.14–5.15.

Рис. 5.14. Отклонение от линейности линеаризованного смесителя (в %)

Рис. 5.15. Логарифмические АЧХ (1) и ФЧХ (2) линеаризованного смесителя

Отклонение от линейности линеаризованного смесителя не превышает 0,7 % при входном напряжении 100 мВ.

Полоса пропускания по уровню -3 дБ составляет 46 ГГц. Столь большой выигрыш в полосе пропускания схемы (рис. 5.13) объясняется тем, что множительное ядро работает при токах, соответствующих максимуму частотных свойств применяемых транзисторов. Токи входных логарифмирующих каскадов выбраны достаточно большими, чтобы выполнялось условие:

![]() .

.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

- Характеристика РЭСИ как объекта теории надежности. Основные показатели безотказности для невосстанавливаемых объектов

- Расчет усилительного резистивного каскада на биполярных транзисторах

- Оценка числовых характеристик случайной погрешности на основе эксперимента

- Электроника

- Теоретические основы построения модуляторов и демодуляторов

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем