Разработка схемы блока арифметико-логического устройства для умножения двух двоичных чисел

Рисунок 3.1 Карты Карно для полного сумматора.

![]() (3.1)

(3.1)

![]() (3.2)

(3.2)

Полученные выражения (3.1) и (3.2) приводим к заданной элементной базе:

![]() (3.3)

(3.3)

![]() (3.4)

(3.4)

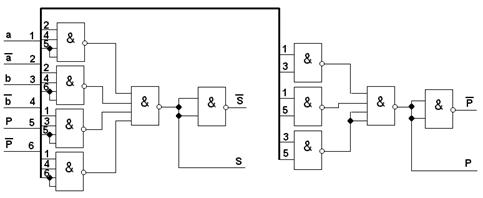

По полученным выражениям строим схему полного сумматора (рис.3.2).

Рисунок 3.2 Принципиальная схема полного сумматора.

Нулевой разряд сумматора для экономии элементов построим по схеме полусумматора. Таблица истинности полусумматора представлена в табл.3.2.

Таблица 3.2

|

А |

B |

S |

Ро |

|

0 |

0 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

По таблице истинности получаем логические выражения:

![]() (3.5)

(3.5)

![]() (3.6)

(3.6)

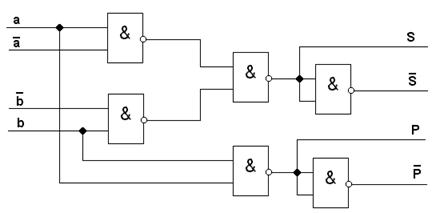

По полученным выражениям строим принципиальную схему (рис.3.3).

Рисунок 3.3 Принципиальная схема полусумматора.

Потребляемую схемой мощность найдем по формуле:

![]() . (3.7)

. (3.7)

где N – количество логических элементов в схеме;

![]() – мощность, потребляемая одним элементом.

– мощность, потребляемая одним элементом.

Количество элементов в схеме равно 83 а мощность элемента – ![]() . Подставляя данные в формулу (3.7) получим:

. Подставляя данные в формулу (3.7) получим:

![]() .

.

Время вычисления будет максимально в случае формирования переноса последовательно в семи младших разрядах сумматора. Таким образом, время счета будет определяться как сумма времени формирования переноса в семи младших разрядах и времени формирования выходного сигнала в старшем разряде:

![]() , (3.8)

, (3.8)

где ![]() – время срабатывания одного логического элемента;

– время срабатывания одного логического элемента;

![]() – максимальный путь (количество последовательно пройденных элементов) формирования переноса в i-ом разряде;

– максимальный путь (количество последовательно пройденных элементов) формирования переноса в i-ом разряде;

![]() – максимальный путь формирования результата в старшем разряде (3 элемента).

– максимальный путь формирования результата в старшем разряде (3 элемента).

Время срабатывания равно 4![]() . Пути

. Пути ![]() для сумматора (разряды 1 – 7) и для полусумматора (разряд 0) равны трём. Тогда по формуле (3.8) получим:

для сумматора (разряды 1 – 7) и для полусумматора (разряд 0) равны трём. Тогда по формуле (3.8) получим:

![]() .

.

3.2 Синтез регистров

Для хранения и сдвига множителя Y и суммы S необходим шестнадцатиразрядный регистр сдвига. Для хранения множимого понадобится один восьмиразрядный регистр RgX.

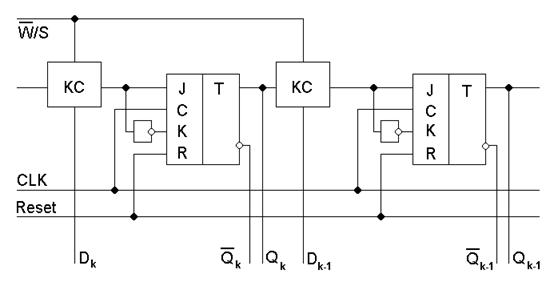

Структурная схема регистра сдвига показана на рис.3.4, из которого видно, что необходимо синтезировать одну комбинационную схему. Таблица истинности для этой схемы представлена в табл. 3.3, где значение управляющего сигнала W/S равное нулю соответствует режиму записи, а равное единице - режиму сдвига на один бит вправо за такт.

Рисунок 3.4 Структурная схема регистра сдвига.

Таблица 3.3

|

D |

Q |

S |

J |

|

X |

0 |

0 |

0 |

|

X |

1 |

0 |

1 |

|

0 |

X |

1 |

0 |

|

1 |

X |

1 |

1 |

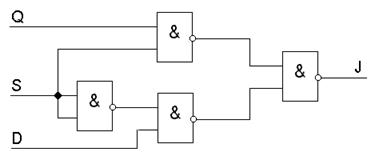

По приведенной таблице истинности находим логические выражения, описывающие работу синтезируемой схемы, и приводим их к заданному базису.

![]() (3.9)

(3.9)

Рисунок 3.5 Схема управления сдвигом.

Принципиальная схема, построенная по выражению (3.9), приведена на рис.3.5.

Восьмиразрядный регистр для хранения Х будет представлять собой восемь JK – триггеров с объединенными тактовыми входами.

Мощность, потребляемую регистрами, определим по формуле

![]() , (3.10)

, (3.10)

где ![]() ,

, ![]() – количество триггеров в регистрах RgX и RgY соответственно;

– количество триггеров в регистрах RgX и RgY соответственно;

![]() – мощность, потребляемая триггером (12 мВт).

– мощность, потребляемая триггером (12 мВт).

![]() - мощность, потребляемая схемой управления сдвигом (8 мВт).

- мощность, потребляемая схемой управления сдвигом (8 мВт).

Подставив численные значения в формулу (3.10), получим:

![]() .

.

Время предустановки регистра равно времени предустановки триггера ![]() , а время задержки – времени задержки триггера

, а время задержки – времени задержки триггера ![]() .

.

3.3 Синтез счётчика

По принципу формирования выходных сигналов счетчики бывают последовательные и параллельные. У первых каждый разряд счётчика устанавливается последовательно вслед за предыдущим. В параллельных счётчиках переключение происходит параллельно всех разрядов. Таким образом, последовательные счётчики имеют задержку кратную разрядности, поэтому могут применяться в устройствах не критичных к быстродействию.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

- Применение контроля информационных слов и их адресов по mod 3 в цифровых устройствах автоматики

- Усилитель низкой частоты для переносной магнитолы

- Разработка технологического процесса сборки автомобильного усилителя мощности

- Конденсатор переменной емкости

- Программная и аппаратная часть автоматизированной сигнализации по GSM каналу

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем