Разработка схемы блока арифметико-логического устройства для умножения двух двоичных чисел

Обозначения управляющих сигналов:

V1 – запись информации в регистр RgX;

V2 – сброс регистра RgY;

V3 – запись информации в регистр RgY;

V4 – разрешение работы счётчика;

V5 – сигнал готовности результата Ready;

По таблице истинности определим функции, описывающие работу КС1 и КС2, и приведем их к заданному элементному базису. Для КС2:

![]() ; (3.20)

; (3.20)

![]() ; (3.21)

; (3.21)

![]() . (3.22)

. (3.22)

Для КС1:

![]() ; (3.23)

; (3.23)

![]() . (3.24)

. (3.24)

Из равенства выражений для сигналов ![]() , и

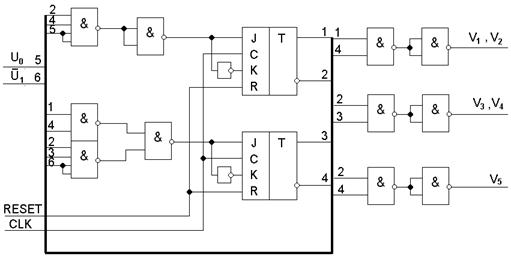

, и ![]() можно сделать вывод, что на этапе проектирования управляющего автомата выявляются возможности оптимизации, упущенные при разработке структурной схемы операционной части. Схема цифрового автомата представлена на рисунке 3.10.

можно сделать вывод, что на этапе проектирования управляющего автомата выявляются возможности оптимизации, упущенные при разработке структурной схемы операционной части. Схема цифрового автомата представлена на рисунке 3.10.

Для реализации цифрового автомата потребуется 13 логических элементов и 2 триггера. Таким образом, мощность потребления определим по формуле

![]() . (3.25)

. (3.25)

Подставляя численные значения, получим:

![]() .

.

Рисунок 3.10 Принципиальная схема управляющего автомата.

Максимальный путь сигнала через комбинационную схему КС1 равен 2-м элементам, и через КС2 – 2-м. Тогда время задержки комбинационных схем определим по формулам:

![]() , (3.26)

, (3.26)

![]() . (3.27)

. (3.27)

По формулам (3.26), (3.27) определим:

![]() ,

,

![]() .

.

Время задержки и время предустановки регистра состояний будет полностью определяться соответствующими параметрами триггеров:

![]() ,

, ![]() .

.

4. ПРОВЕРКА РАСЧЕТНЫХ ПАРАМЕТРОВ НА СООТВЕТСТВИЕ КОНСТРУКТИВНЫМ ТРЕБОВАНИЯМ

4.1 РАСЧЕТ ТАКТОВОГО СИГНАЛА

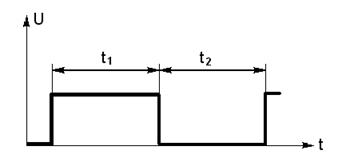

Временная диаграмма тактового сигнала представлена на рисунке 4.1.

Рисунок 4.1 Временная диаграмма тактового сигнала.

Устройство управления (триггеры регистра состояния) тактируются по фронту, а операционная часть – по спаду (тактовый сигнал на входы триггеров операционной части подаются через элементы 2И-НЕ). Таким образом, длительность активной фазы сигнала ![]() будет определяться быстродействием устройства управления, а фазы

будет определяться быстродействием устройства управления, а фазы ![]() – быстродействием операционной части и комбинационной схемы КС1.

– быстродействием операционной части и комбинационной схемы КС1.

Определяющим фактором длительности вычислений устройства управления является готовность управляющих сигналов. Поэтому интервал времени ![]() будет определяться временем задержки срабатывания схемы КС2, временем предустановки регистра и временем задержки регистра:

будет определяться временем задержки срабатывания схемы КС2, временем предустановки регистра и временем задержки регистра:

![]() . (4.1)

. (4.1)

Подставим в формулу (4.1) численные значения входящих величин, определенные выше:

![]() .

.

Наибольшее время для вычисления в операционной части потребуется в состоянии ![]() , так как в этом состоянии производится суммирование, требующее значительно больших затрат времени по сравнению с другими операциями. Интервал времени

, так как в этом состоянии производится суммирование, требующее значительно больших затрат времени по сравнению с другими операциями. Интервал времени ![]() будет определяться временем задержки логического элемента, инвертирующего тактовый сигнал, временем установки регистра RgY и временем формирования бита переноса в сумматоре:

будет определяться временем задержки логического элемента, инвертирующего тактовый сигнал, временем установки регистра RgY и временем формирования бита переноса в сумматоре:

![]() . (4.2)

. (4.2)

Подставив численные значения, получим:

![]() .

.

Теперь нетрудно определить период тактового сигнала:

![]() .

.

4.2 ОПРЕДЕЛЕНИЕ МАКСИМАЛЬНОГО ВРЕМЕНИ ВЫЧИСЛЕНИЯ

Максимальное время вычисления определим по формуле

![]() , (4.3)

, (4.3)

где ![]() – максимальное количество тактов.

– максимальное количество тактов.

При умножении целых чисел методом последовательного суммирования максимальное количество тактов будет определяться величиной множителя Y. Для восьмиразрядного множителя при совмещении операций сложения и сдвига в один такт максимальным значением является восемь. Помимо этих 8 тактов понадобится один такт для начальной установки регистров и счетчика (состояние ![]() ) и еще один такт для установки сигнала READY по окончании счета. Следовательно, общее число тактов

) и еще один такт для установки сигнала READY по окончании счета. Следовательно, общее число тактов![]() , а максимальное время вычисления

, а максимальное время вычисления

![]() или

или ![]() .

.

Полученное значение меньше заданного ограничения 2 мкс.

4.3 ОПРЕДЕЛЕНИЕ ПОТРЕБЛЯЕМОЙ МОЩНОСТИ

Потребляемая устройством мощность будет равна сумме мощностей, потребляемых всеми ее составными частями (регистры X и Z, счетчик, сумматор, схема сравнения, три логических элемента 2И-НЕ и устройство управления):

![]() . (4.4)

. (4.4)

Подставляя численные значения, получим потребляемую устройством мощность:

![]() .

.

Реальная потребляемая мощность оказалась меньше заданного ограничения 1000 мВт.

ЗАКЛЮЧЕНИЕ

В результате выполнения данного курсового проекта был разработан блок АЛУ для умножения двух положительных двоичных чисел. Все требования, оговоренные в техническом задании, были выполнены.

Разработанное устройство имеет по 8 входов для множителя Y0 – Y7 и множителя X0 – X7, вход разрешения начала счета START с активным уровнем "1", вход принудительного сброса с активным уровнем "1" и вход синхронизации с тактированием по фронту импульса; 16 выходов результата Z0 – Z15 и выход готовности результата READY с активным уровнем "1".

Максимальное время счета ![]() .

.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем