Программно-аппаратный комплекс для проведения специальных комплексных проверок электронных устройств

Регистр памяти данных (РПД) предназначен для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт. Кроме того, к адресному пространству РПД примыкают адреса РСФ.

РСФ состоит из нескольких регистров, используемых для фиксации и программного изменения управляющих битов и битов состояния схемы прерывания, таймера-счетчика, приемоперед

атчика последовательного порта и для управления мощностью электропитания микроконтроллера.

Кварцевый резонатор, подключаемый к выводам корпуса МК 1880ВЕ31У, обеспечивает стабильность частоты внутреннего генератора, который, в свою очередь, формирует сигналы синхронизации. Устройство управления (УУ) на основе сигналов синхронизации формирует машинный цикл фиксированной длительности, равной 12 периодам резонатора или шести состояниям первичного управляющего автомата (каждое состояние управляющего автомата содержит две фазы сигналов резонатора).

Большинство команд микроконтроллера выполняется за один машинный цикл. Некоторые команды, оперирующие с двухбайтными словами или связанные с обращением к внешней памяти, выполняются за два машинных цикла. Только команды деления и умножения требуют четырех машинных циклов.

Восьмибитное АЛУ может выполнять арифметические операции сложения, вычитания, умножения и деления; логические операции И, ИЛИ, исключающее ИЛИ, а также операции циклического сдвига, сброса, инвертирования и т.п. В АЛУ имеются программно недоступные регистры Т1 и Т2, предназначенные для временного хранения операндов, схема десятичной коррекции и схема формирования признаков.

АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (семь для данных и четыре для адресов), то путем комбинирования «операция-режим адресации» базовое число команд 111 (50 из которых однобайтные, 45-двубайтные, 16-трехбайтные) расширяется до 255 из 256 возможных при однобайтном коде операции.

Блок таймеров/счетчиков предназначен для подсчета внешних событий, получения программно-управляемых временных задержек, выполнения времязадающих функций.

Блок последовательного интерфейса и прерываний предназначен для организации ввода-вывода последовательных потоков информации и организации системы прерывания программ.

Программный счетчик предназначен для формирования текущего 16-ти разрядного адреса внешней памяти программ.

Порты ввода-вывода предназначены для ввода или вывода информации побайтно. Каждый порт содержит управляемый регистр-защелку, входной буфер и выходной драйвер.

Двунаправленный порт Р0 и квазидвунаправленные порты Р1, Р2, Р3 являются портами ввода/вывода и предназначены для обмена информацией МК с внешними устройствами, образуя 32 линии ввода/вывода.

Память данных предназначена для приема, хранения информации, используется в процессе выполнения программ.

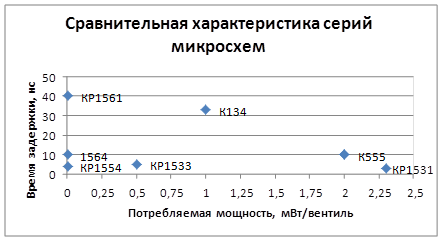

3.2.3 Электрическая принципиальная схема ПАК разработана с использованием микросхем серии 1554 отечественного производства [8]. Она была выбрана по результатам сравнительной характеристики серий микросхем, представленной на рис.1.Так, в сочетании с высоким быстродействием, микросхемы серии КР1554 обладают низкой потребляемой мощностью и большой нагрузочной способностью. Что позволяет разработчикам аппаратуры существенно улучшить технические и технико-экономические характеристики разрабатываемых изделий.

Микросхемы серии КР1554 изготавливаются по 1.4 мкм КМОП технологии с окисной изоляцией, поликремневым затвором. Используется двухуровневая металлизация, которая позволяет наряду с уменьшением размеров кристалла получить уменьшение амплитуды помех по шинам земли и питания. Серия 1554 микросхем обладает следующими характеристиками:

– низкая потребляемая мощность - 0,0025 мВт/вентиль при частоте переключения 1 МГц (характерно для микросхем, изготовленных по КМОП технологии, в отличие от ТТЛШ, которые имеют ток потребления в статическом режиме на три порядка больше - 1,2 мВт/вентиль на этой частоте)

– высокое быстродействие время задержки распространения 4 нс;

– работоспособность в широком диапазоне напряжений питания от 3,3 до 5,5 В, чем не обладают биполярные микросхемы (4,5 – 5,5 В);

– относятся к помехоустойчивым сериям микросхем, что снижает стоимость оборудования, т.к. позволяет снизить затраты на обеспечение необходимых гальванических развязок, и других мер защиты от помех, а также облегчает требования к топологии печатных плат;

– низкие значения входных токов (доли микроампер) и мощные выходные каскады, обеспечивающие выходные токи в десятки миллиампер, что позволяет подключать к ним нагрузки и без дополнительного усилителя сигнала. Это повышает надежность систем, т.к. не требуются дорогостоящие стабилизированные источники питания большой мощности, теплоотводы и т.д.

Микросхема 1554 ИР22 – восьмиразрядный регистр на D-триггерах с потенциальным входом C. Выходные буферные каскады микросхемы устанавливаются в третье состояние, если на вход разрешения состояния высокого импеданса EZ подано напряжение высокого уровня. Используется в качестве регистра-защелки для того чтобы было возможно использовать адреса А0-А7, которые убираются с линий порта Р0, давая возможность вести обмен данными. Третье состояние используется для отключения устройства, что необходимо для нормальной работы шины, так как только одно устройство может выставлять данные на магистраль.

Микросхема 1554 ИР23 – восьмиразрядный управляемый по фронту регистр с параллельным вводом-выводом данных с тремя состояниями на выходе. Регистр на D-триггерах с динамическим входом С. Выходные буферные каскады микросхемы устанавливаются в третье состояние, если на вход разрешения состояния высокого импеданса EZ подано напряжение высокого уровня. Два регистра с асинхронной записью информации 1554ИР23 представляют собой ячейки оперативной памяти. Каждой ячейке оперативной памяти соответствует одно реле (один ключ), отвечающий за подключения питания на тестируемые цепи.

Микросхема 1554 ТЛ2 содержит шесть идентичных логических элементов со стандартными активными выходами, выполняющих Булеву функцию ![]() .

.

Наличие на входах элементов гистерезиса позволяет использовать микросхему в качестве формирователя сигналов.

Микросхема 1554ЛИ1 состоит из четырех независимых логических вентилей в одном корпусе, выполняющих функцию 2И.

Микросхема 1554 КП7 представляет собой селектор-мультиплексор из 8 в 1 и в зависимости от установленного на входах SED1 – SED3 кода разрешает прохождение сигнала на выходы Y и не Y только от одного из восьми информационных входов D0 – D7, при этом на входе разрешения выбора данных должно быть установлено напряжение низкого уровня. Выбор этой микросхемы основывается именно на количестве и назначении выводов (из 8 в 1), так как нам необходимо получить сигнал от одной из 8 цепей. Так как общее количество тестируемых цепей 16, то используем две микросхемы и задействуем два порта МК.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем