Анализ алгоритма работы специализированного вычислителя

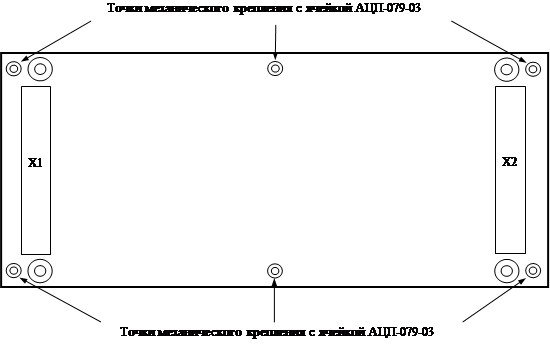

Электрическое соединение разрабатываемой системы с платой АЦП-079-03 будет осуществляться при помощи этих разъемов (Х1, Х2).

Входными сигналами системы регистрации данных являются:

- шины питания (может использоваться вся номенклатура питающих напряжений);

- последовательный байтный порт микропроцессора LINK (LN0 – LN12).

Исходя из анализа цепей в соединителях Х1 и Х2 получаем

, что все требуемые сигналы находятся на разъеме Х2, следовательно разъем Х1 будет использоваться только для дублирования цепей корпуса и в качестве механического соединителя. В таблице 1.6 приведены контакты разъема Х2 разрабатываемой ячейки и сигналы соответствующие им, которые предполагается использовать для связи с ячейкой АЦП-079-03.

Так как разрабатываемая ячейка будет использоваться в составе специализированного вычислителя необходимо обеспечить дополнительное механическое крепление. Следовательно нужно обеспечить совместимость системы регистрации данных и ячейки АЦП-079-03 по местам механического крепления. Для осуществления механического крепления ячеек в составе изделия необходимо использовать крепеж (болты, домкраты) большей длинны.

Так как разрабатываемая ячейка будет использоваться в составе специализированного вычислителя необходимо обеспечить дополнительное механическое крепление. Следовательно нужно обеспечить совместимость системы регистрации данных и ячейки АЦП-079-03 по местам механического крепления. Для осуществления механического крепления ячеек в составе изделия необходимо использовать крепеж (болты, домкраты) большей длинны.

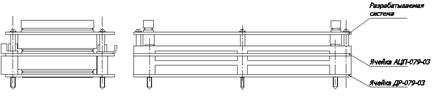

Эскиз системы в составе специализированного вычислителя представлен на рисунке 1.3.

Рисунок 1.4 – Эскиз механического крепления системы в специализированном вычислителе.

2. РАЗРАБОТКА ФУНКЦИОНАЛЬНОЙ СХЕМЫ И ВЫБОР ЭЛЕМЕНТНОЙ БАЗЫ

2.1 Описание функциональной схемы системы

Для того чтобы выполнить данную задачу нам необходимо иметь следующие узлы:

– узел приема информации из коммуникационного порта ввода/вывода микропроцессора 1879ВМ1;

– блок обмена с последовательным портом;

– блок обмена с буферной памятью;

– скоростная буферная память;

– блок согласования с микроконтроллером;

– блок обмена с часами реального времени;

– блок обмена с основным накопителем;

– микроконтроллер;

– накопитель.

2.1.1 Узел приема информации из коммуникационного порта ввода/вывода микропроцессора 1879ВМ1

Информация поступает с темпом 20 Мбайт/сек, т.е. период обновления информации 50 нс. В дальнейшем эту информацию необходимо сохранять в накопителе. Для обеспечения необходимого объема регистрируемой информации (8 Гб) в приемлемых геометрических размерах целесообразно применять твердотельные накопители на базе микросхем Flash или малогабаритные жесткие диски. Так как разрабатываемый блок будет использоваться в жестких климатических и механических условиях, в которых не могут работать жесткие диски, то будет использоваться твердотельный накопитель. Современные накопители большого объема на базе микросхем Flash памяти не способны обеспечить высокий темп записи, следовательно, нам необходима промежуточная скоростная память. Объем данной промежуточной памяти должен быть выше, чем единичный пакет информации, передаваемой за один обмен. Принятый пакет данных, сохраненный в промежуточной буферной памяти, необходимо переписать в основной накопитель до прихода следующей пачки информации (33 мс).

Исходя из условий технического задания для управления нашей системой и обеспечения связи с ПК нам необходим микроконтроллер со встроенным USB-интерфейсом. Но микроконтроллер не сможет обеспечить достаточного быстродействия. Поэтому для перезаписи данных из промежуточной буферной памяти в основной накопитель необходимо использовать аппаратный автомат перезаписи данных, которым будет управлять микроконтроллер.

Для синхронизации информации с разрабатываемого блока с другими приборами регистрации, а так же для привязки информации нам необходимы часы реального времени, они позволят регистрировать время прихода нового пакета информации от специализированного вычислителя. Тем самым мы показали необходимость пяти блоков: микроконтроллера, промежуточной буферной памяти, основного накопителя большого объема, автомата перезаписи данных из промежуточной буферной памяти в основной накопитель и часов реального времени. Для того, чтобы связать все узлы между собой необходимо согласовать интерфейсы. Для функции согласования нам необходимы узлы которые за это отвечают.

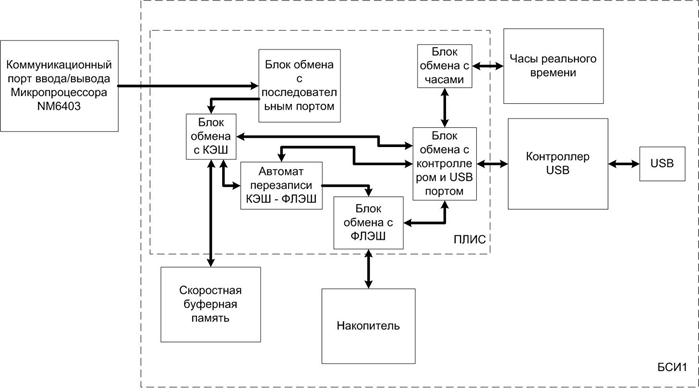

На основе данных рассуждений мы получаем функциональную схему, приведенную на рисунке 2.1.

Рисунок 2.1 – Функциональная схема разрабатываемой системы

2.1.2 Блок обмена с последовательным портом

Блок обмена с последовательным портом принимает информацию от специализированного вычислителя по коммуникационному порту ввода/вывода микропроцессора 1879ВМ1 и передает ее в блок обмена с промежуточной буферной памятью. Данный блок содержит следующие входные сигналы:

– восьмиразрядную шину данных;

– один сигнал – строб готовности данных;

– один сигнал приема данных.

Выходные сигналы блока:

– шина адреса;

– шина данных;

– сигнал записи данных;

– сигнал ответа для коммуникационного порта.

Данный блок выполняет следующие функции:

– принимает информацию ;

– синхронизирует принятую информацию с тактовым генератором;

– формирует сигнал ответа для коммуникационного порта ввода/ вывода микропроцессора 1879ВМ1 о том, что данные приняты, который необходим для функционирования интерфейса LINK;

– ведет подсчет принятых байт информации для формирования сигнала окончания сеанса обмена со специализированным вычислителем;

– формирует шину данных, шину адреса, сигнал записи для работы с промежуточной буферной памятью;

– формирует сигнал окончания сеанса обмена.

2.1.3 Блок обмена с буферной памятью

Данный блок служит для преобразования интерфейса скоростной буферной памяти и обеспечивает три следующих режима работы памяти:

– запись принятой информации, поступающей от блока обмена с последовательным портом в скоростную буферную память;

– предоставление доступа микроконтроллеру к скоростной буферной памяти;

– предоставление автомату перезаписи доступа к скоростной буферной памяти для считывания полученных данных.

В блок поступают сигналы:

– от блока обмена по последовательному интерфейсу:

1) шина адреса;

2) шина данных;

3) сигнал записи;

– от блока обмена микроконтроллера:

1) входная шина данных;

2) шина адреса;

3) сигналы чтения;

4) сигнал записи;

5) сигналы управления режимом работы блока;

– от автомата перезаписи информации из буферной памяти в накопитель:

1) шина адреса;

2) сигнал чтения;

– из блока выходят сигналы:

1) шина данных для автомата перезаписи и микроконтроллера;

2) шина адреса для буферной памяти;

3) двунаправленная шина данных для буферной памяти;

4) сигналы управления буферной памятью.

2.1.4 Скоростная буферная память

Это обычная статическая память объёмом до 0,5 М со временем выборки до 25 нс и быстрее. Данный блок напрямую работает только с блоком обмена с буферной памятью (блок преобразования интерфейса).

Другие рефераты на тему «Физика и энергетика»:

Поиск рефератов

Последние рефераты раздела

- Автоматизированные поверочные установки для расходомеров и счетчиков жидкостей

- Энергосберегающая технология применения уранина в котельных

- Проливная установка заводской метрологической лаборатории

- Источники радиации

- Исследование особенностей граничного трения ротационным вискозиметром

- Исследование вольт-фарадных характеристик многослойных структур на кремниевой подложке

- Емкость резкого p-n перехода