Анализ алгоритма работы специализированного вычислителя

Для обеспечения конфигурирования ПЛИС совместим две стандартные схемы конфигурирования, рекомендованные фирмой производителем (ALTERA). Первая схема конфигурации (JTAG-цепочка) позволяет независимо загружать прошивку в конфигурационную микросхему и ПЛИС. Она используется на этапе настройки, проверки и конфигурирования загрузочной памяти. Вторая цепочка (режим пассивной последовательной конфиг

урации) используется в штатной работе ячейки. При включении питания при ее помощи информация из конфигурационной микросхемы переписывается в ПЛИС.

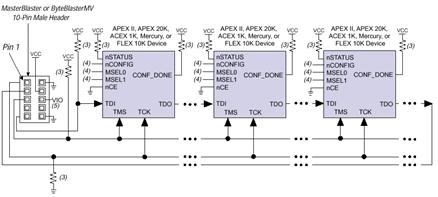

Элементы D1, D2 образуют JTAG-цепочку, организованную для загрузки элементов в системе. Кроме того JTAG, являясь стандартом периферийного сканирования, позволяет осуществлять проверку (верификацию) загруженной конфигурации ПЛИС и конфигурационного ПЗУ. Схема включения данных элементов подчиняется схеме функционирования JTAG-цепочки /3/ (рисунок 3.1).

Рисунок 3.1 – Схема функционирования JTAG-цепочки

Все резисторы схемы функционирования JTAG-цепочки выбраны номиналом 1 кОм, согласно рекомендации фирмы ALTERA.

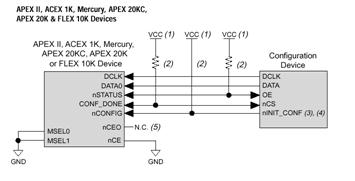

На рисунке 3.2 представлена схема для пассивной последовательной конфигурации.

Рисунок 3.2 – Схема для пассивной последовательной конфигурации

Все резисторы схемы для пассивной последовательной конфигурации (рисунок 3.2) выбраны номиналом 1 кОм, согласно рекомендации фирмы ALTERA.

Характеристики выводов конфигурирования приведены в таблице 3.2.

Таблица 3.2 – Перечень характеристик выводов конфигурирования микросхемы ПЛИС

|

Название вывода |

Тип вывода |

Описание |

|

MSEL0 MSEL1 |

Вход |

Двухбитовый вход конфигурации. |

|

nSTATUS |

Двунаправленный, открытый сток |

Микросхема устанавливает логический "0" на выводе сразу же после включения питания и снимает его не позже чем через 5 мкс (при использовании конфигурационной микросхемы она удерживает логический "0" на выводе nSTATUS в течение 200 мс). Напряжение на выводе nSTATUS должно подтягиваться к напряжению VCC при помощи нагрузочного резистора сопротивлением1 кОм. При обнаружении ошибки конфигурирования вывод nSTATUS устанавливается конфигурируемой ПЛИС в логический "0". Во время конфигурирования или инициализации установка внешней схемой логического "0" на выводе nSTATUS не влияет на конфигурируемую ПЛИС. При использовании конфигурационной микросхемы логический "0" на выводе nSTATUS вызовет попытку конфигурации ПЛИС конфигурационной микросхемой. |

|

nCONFIG |

Вход |

Вход управления конфигурацией. Логический "0" – сбрасывает конфигурируемую микросхему. Конфигурирование начинается по положительному перепаду. При логическом "0" на nCONFIG все I/O-выводы находятся в третьем состоянии. |

|

DCLK |

Вход |

Вход тактового синхросигнала конфигурируемой ПЛИС от внешнего источника. В PSA или PPA-схемах конфигурирования на выводе DCLK должна быть логическая "1", для исключения неопределенного состояния. |

|

nCE |

Вход |

Выбор микросхемы уровнем логического "0". Логический "0" на выводе nCE выбирает микросхему для запуска конфигурирования. Во время конфигурирования одной микросхемы на выводе должен оставаться логический "0". Уровень логического "0" должен быть на nCE во время конфигурации, инициализации и пользовательского режима |

|

nCEO |

Выход |

Выход переходит в логический "0" после выполнения конфигурирования. Используется в схемах с несколькими конфигурируемыми микросхемами. |

|

DATA0 |

Вход |

Вход данных. В последовательных режимах конфигурирования, на вывод DATA0 подаются битовые конфигурационные данные ПЛИС. |

|

TDI |

Вход |

Выводы JTAG. При использовании этих выводов как пользовательских I/O-выводов, до и во время конфигурирования, их состояния должны сохраняться неизменными. Это необходимо для исключения возможности загрузок случайных JTAG-инструкций. |

|

TDO |

Выход | |

|

TMS |

Вход | |

|

TCK |

Вход | |

|

CONF_DONE |

Выход, открытый сток |

Выход статуса. Может использоваться для сигнализации того, что микросхема инициализирована, и находиться в режиме заданным пользователем. Во время конфигурирования на выводе CONF_DONE устанавливается логический "0". До и после конфигурирования, вывод CONF_DONE освобождается и напряжение на нем подтягивается |

|

к напряжению VCC с помощью внешнего нагрузочного резистора. До конфигурации CONF_DONE находится в третьем состоянии, поэтому он подтягивается к логической "1" при помощи внешнего нагрузочного резистора. Таким образом, для определения состояния микросхемы необходимо обнаружить переход из логического "0" в логическую "1". Эта опция устанавливается в САПР QUARTUS II. |

3.2 Контроллер обмена с USB каналом

При построении ПЭС нам необходимо решить три задачи:

– режим работы с внешней памятью, при этом часть двунаправленных портов ввода вывода становятся шинами адреса, шинами данных и сигналами управления. Данный режим нам необходим для согласования микроконтроллера с внешними устройствами;

– необходимо согласовать контроллер с USB интерфейсом;

– для управляющего контроллера необходимо обеспечить загрузку программы во внутреннюю Flash-память.

Для обеспечения второго и третьего перечислений необходимо применить стандартные решения, предложенные разработчиком. Для этого воспользуемся схемой, предложенной в /1/ и представленной на рисунке 3.3.

Так же по третьему перечислению необходимо отметить, что внутри контроллера существует два загрузчика: пользовательский и аппаратный (HBL, Hadware BootLoader). Пользовательский загрузчик позволяет запускать программы, записанные в память микроконтроллера, а аппаратный позволяет осуществить запись самой программы. В данной схеме перевести контроллер в режим программирования (записи программы) можно выполнив следующую последовательность действий:

Другие рефераты на тему «Физика и энергетика»:

Поиск рефератов

Последние рефераты раздела

- Автоматизированные поверочные установки для расходомеров и счетчиков жидкостей

- Энергосберегающая технология применения уранина в котельных

- Проливная установка заводской метрологической лаборатории

- Источники радиации

- Исследование особенностей граничного трения ротационным вискозиметром

- Исследование вольт-фарадных характеристик многослойных структур на кремниевой подложке

- Емкость резкого p-n перехода