Анализ алгоритма работы специализированного вычислителя

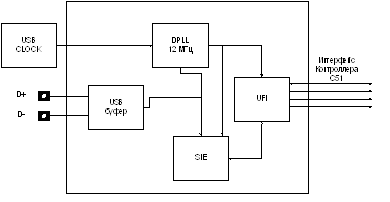

Рисунок 2.2 – Структурная схема USB модуля микроконтроллера АТ89С5131

Микросхема RTC4543 является микросхемой часов реального времени. Данная микросхема имеет способность сохранять данные в очень широком диапазоне напряжений, кроме того, в неактивном режиме имеет крайне малое энергопотребление, что позволяет применять дл

я поддержания их работоспособности батареи малых габаритов. Микросхема часов обладает следующими характеристиками:

– точность работы часов (макс.) – 1 мин/мес. при температуре 25 °С;

– температурный рабочий диапазон – от минус 40 до +85 °С;

– время доступа к данным памяти – от 70 нс;

– напряжение питания – от 2,5 до 5,5 В;

– коррекция хода календаря на 100 лет;

– автоматическая коррекция високосного года.

В качестве скоростной буферной памяти будет использована микросхема IDT71V424S15YI, которая представляет собой высокоскоростное статическое ОЗУ организованное 512 к × 8 бит. Она произведена по фирменной высокопроизводительной и очень надежной технологии фирмы Integrated Device Technology (IDT). В неактивном режиме имеет низкое энергопотребление. Основные характеристики микросхемы:

– минимальная длительность сигнала записи – 15 нс;

– время выборки адреса – не более 12 нс;

– напряжение питания 3,3 В;

– время перехода в активный/неактивный режим – 6 нс;

– температурный диапазон хранения данных – от минус 55 до +125 °С.

Цифровая часть системы выполнена на базе ПЛИС. Это удобная в освоении и применении элементная база, альтернативы которой в данном случае не существует. Последние годы характеризуются резким ростом плотности упаковки элементов на кристалле и резким падением цен на ПЛИС, что позволило широко применять ПЛИС в системах обработки сигналов. Высокое быстродействие и упаковка на кристалле достаточного объёма памяти однозначно определили выбор ПЛИС.

В разработанной системе применена микросхема ПЛИС EPF10K30AQI240-3 фирмы Altera Corporation семейства FLEX 10KA. Такой выбор обусловлен тем, что семейство FLEX10KA является наиболее доступным. Только это семейство имеет градацию скорости 3, которая удовлетворяет необходимым требованиям. Выбранная ПЛИС имеет 6 встроенных блоков памяти емкостью 2048 бит, корпус TQFP-240 коммерческого исполнения. Напряжение питания микросхемы EPF10K30AQI240-3 составляет +3,3 В. Данная микросхема обеспечивает достаточное быстродействие и обладают необходимым для системы регистрации данных объемом встроенных блоков памяти ЕАВ. Микросхемы EPF10K30AQI240-3 поддерживает программирование и реконфигурирование в системе, это означает, что программирование проходит в составе системы без использования программатора на смонтированной плате, причем программирование ПЛИС или конфигурационного ПЗУ может производиться многократно. Программирование производится по стандартному JTAG интерфейсу (используется стандарт IEEE Std. 1149.1-1990). Для программирования и загрузки конфигурации ПЛИС используется кабель ByteBlasterMV.

Так как выбранная микросхема ПЛИС выполнена по технологии SRAM, требующей загрузки конфигурации при включении питания, в системе необходимо использовать конфигурационное ПЗУ. В качестве конфигурационного ПЗУ была выбрана микросхема EPC2TI32, которая, так же как и ПЛИС, поддерживает программирование в системе по стандарту JTAG.

Основной накопитель выполнен на базе микросхемы ФЛЭШ K9K49G08U0M емкостью 4 Гбит с резервом емкостью 128 Мбит организованы как 512 М × 8 бит. Технология И-НЕ обеспечивает наилучшее соотношение «цена-качество» на рынке полупроводниковых запоминающих устройств. Операция записи страницы объемом 2112 байт может быть выполнена за 200 мкс. Операция стирания блока объемом 128 Кбайт может быть выполнена за 2 мс. Данные со страницы данных могут быть прочитаны циклами по 30 нс на байт. Выводы I/O служат как двунаправленный порт для ввода команд, адреса и ввода/вывода данных. Внутренний контроллер записи автоматизирует все функции записи и стирания, включая частоту повторения импульсов там, где это необходимо, а также внутреннюю верификацию и ограничение данных. Даже интенсивно записывающие системы могут воспользоваться преимуществами расширенной достоверности 100 Kциклов записи/стирания K9K4G08U0M, обеспечивая ЕСС (код исправления ошибок) по алгоритму отображения в реальном времени. Микросхемы K9K4G08U0M являются оптимальным решением для применения в разрабатываемой системе регистрации данных в качестве твердотельного накопителя большого объема памяти.

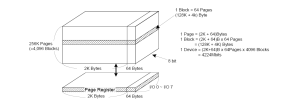

Микросхема K9K4G08U0M – это память объемом 4224 Мбит, организованная как 262144 строки (страницы) по 2112×8 столбцов. Запасные 64 столбца находятся по адресам начатая с 2048 по 2111. 2112-ти байтовый регистр данных и 2112-ти байтовый кэш-регистр последовательно соединен с остальными. Эти последовательно соединенные регистры соединены с массивом ячеек памяти, для согласования передачи данных между I/O буферами и ячейками памяти при операции чтения или записи страницы. Массив памяти складывается из 32-х ячеек, последовательно соединенных для формирования И-НЕ структуры. Каждая из 32 ячеек находятся на различных страницах. Блок состоит из 2 строк с И-НЕ структурой. И-НЕ структура состоит из 32 ячеек. Всего в блоке 1081344 И-НЕ ячеек. Операции чтения и записи выполняются постранично, тогда, как операция стирания выполняется поблочно. Массив памяти состоит из 4096 отдельно стираемых блоков объемом 128 Кбайт. Структура микросхемы K9K4G08U0M приведена на рисунке 2.3.

Рисунок 2.3 – Структура микросхемы K9K4G08U0M

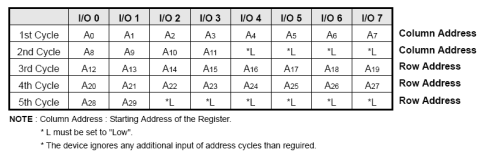

Адрес K9K4G08U0M мультиплексирован на 8 выводов (таблица 2.1). Такая схема существенно уменьшает число выводов и допускает дальнейшее повышение плотности с сохранением согласованности на системной плате. Команды, адрес и данные записываются через входы/выходы переводом WE в низкий уровень при низком уровне на входе СЕ. Данные сохраняются по фронту сигнала WE. Сигналы разрешение записи команды (CLE) и разрешение записи команды адреса (ALE) используются для мультиплексирования команд и адреса соответственно из приходящих на входы/выходы данных. Некоторые команды требуют одного шинного цикла, например, команда сброса, команда чтения состояния и т.д. Для других команд, таких как чтение страницы, стирание блока и запись страницы, необходимо 2 цикла: один на установку и другой – на исполнение команды. 512 Мбайт физического объема требуют 30-разрядного адреса, таким образом, необходимо 5 циклов записи адреса: 2 цикла для адресации по столбцам (Column) и 3 цикла для адресации по строкам (Row).

Таблица 2.1 – Адресация микросхемы K9K4G08U0M

Для операции чтения и записи страницы так же необходимы 5 циклов записи адреса, следующие за нужной командой. Однако для операции стирания блока требуется всего 3 цикла записи адреса (адрес страницы). Операции с устройством выбираются записью специальных команд в командный регистр (таблица 2.2).

Другие рефераты на тему «Физика и энергетика»:

Поиск рефератов

Последние рефераты раздела

- Автоматизированные поверочные установки для расходомеров и счетчиков жидкостей

- Энергосберегающая технология применения уранина в котельных

- Проливная установка заводской метрологической лаборатории

- Источники радиации

- Исследование особенностей граничного трения ротационным вискозиметром

- Исследование вольт-фарадных характеристик многослойных структур на кремниевой подложке

- Емкость резкого p-n перехода