Автоматизация измерений, контроля и испытаний

|

Рис. 4 |

Таблица 2

|

Данный элемент выпускается в виде интегральных схем (ИС) типа ЛП5 (серии 133, 155, 530, 531, 533, 555, 1531, 1533); ЛП12 (555); ЛП107 (100, 500, 1500); ЛП2 (561, 564); ЛП14 (1561) и т. п.

Реализуем четвертьсумматор в базисах И-НЕ, ИЛИ-НЕ и с использованием только одного инвертора, для чего преобразуем уравнение (5):

![]() (6)

(6)

|

(7) | ||

|

|

(8) | |

Схемы, полученные по уравнениям (6)–(8), приведены на рис. 5.

![]()

Рис. 5

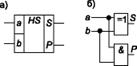

Полусумматор (рис. 6) имеет два входа a и b для двух слагаемых и два выхода: S — сумма, P — перенос. Обозначением полусумматора служат буквы HS (half sum — полусумма). Работу его отражает таблица истинности 2 (табл. 3), а соответствующие уравнения имеют вид:

|

|

(9) |

|

Рис. 6 |

Таблица 3

|

Из уравнений (9) следует, что для реализации полусумматора требуется один элемент “исключающее ИЛИ” и один двухвходовый вентиль И (рис. б).

Полный одноразрядный двоичный сумматор

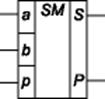

Он (рис. 7) имеет три входа: a, b — для двух слагаемых и p — для переноса из предыдущего (более младшего) разряда и два выхода: S — сумма, P — перенос в следующий (более старший) разряд. Обозначением полного двоичного сумматора служат буквы SM. Работу его отражает таблица истинности 3 (табл. 4).

|

Рис. 7 |

Таблица 4

|

Уравнения, описывающие работу полного двоичного сумматора, представленные в совершенной дизъюнктивной нормальной форме (СДНФ), имеют вид:

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

- Аналоговые перемножители напряжения

- Оптические средства обнаружения

- Приёмник радиовещательный карманный

- Разработка системы управления освещением при помощи любого пульта дистанционного управления от бытовой аппаратуры

- Гибкие производственные линии (ГПЛ) механообрабатывающего производства корпусных деталей

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем