Создание информационно-справочной подсистемы САПР конструкторско-технологического назначения. Дискретные элементы

Таблица 2.4 – Функциональная таблица (таблица истинности) И-НЕ

|

А |

B |

Q |

|

0 |

0 |

1 td> |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

![]() Недостаток схемы - при подаче на входы A и В одновременно напряжений логических 1 схема потребляет ток от источника питания. Если же элемент И-НЕ выполнен на КМОП-транзисторах, то этого не происходит. В частности, на рис. 2.9, б дается схема подобного элемента. Транзисторы VT1 и VT2 имеют р-каналы, вследствие чего, когда на их затворах (входах A, В) действуют сигналы логических 0, они полностью открыты и на выходе Q имеется положительное напряжение логической 1. При этом транзисторы VT3 и VT4 полностью заперты, ибо имеют n-каналы. Когда на оба входа A, В одновременно действуют положительные напряжения логических 1, транзисторы VT1 и VT2 запираются и напряжение с выхода Q снимается. При этом транзисторы VT3 и VT4 отпираются и выход оказывается соединенным с общим проводом через малое сопротивление (500 - 1000 Ом). Если на одном из входов действует напряжение логического 0, а на другом - напряжение логической 1, то один из транзисторов с р - каналом (VT1 или VT2) запирается, но другой остается открытым, и поскольку они включены параллельно, на выходе остается напряжение логической 1.

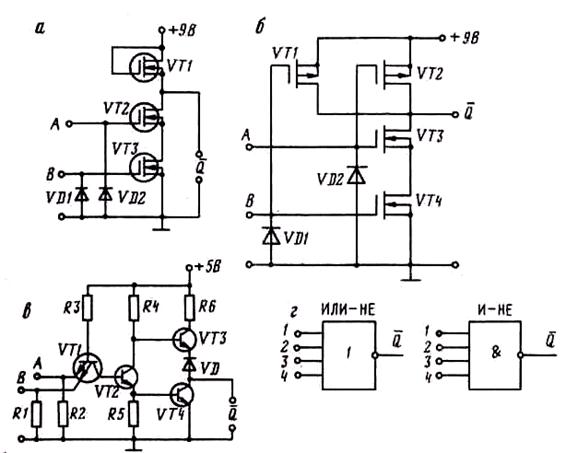

Недостаток схемы - при подаче на входы A и В одновременно напряжений логических 1 схема потребляет ток от источника питания. Если же элемент И-НЕ выполнен на КМОП-транзисторах, то этого не происходит. В частности, на рис. 2.9, б дается схема подобного элемента. Транзисторы VT1 и VT2 имеют р-каналы, вследствие чего, когда на их затворах (входах A, В) действуют сигналы логических 0, они полностью открыты и на выходе Q имеется положительное напряжение логической 1. При этом транзисторы VT3 и VT4 полностью заперты, ибо имеют n-каналы. Когда на оба входа A, В одновременно действуют положительные напряжения логических 1, транзисторы VT1 и VT2 запираются и напряжение с выхода Q снимается. При этом транзисторы VT3 и VT4 отпираются и выход оказывается соединенным с общим проводом через малое сопротивление (500 - 1000 Ом). Если на одном из входов действует напряжение логического 0, а на другом - напряжение логической 1, то один из транзисторов с р - каналом (VT1 или VT2) запирается, но другой остается открытым, и поскольку они включены параллельно, на выходе остается напряжение логической 1.

При этом один из транзисторов с n-каналом (VT3 или VT4) оказывается открытым; другой - закрытым, и, поскольку они включены последовательно, шунтирования выхода Q малым сопротивлением не происходит и напряжение на выходе оказывается высоким. Таким образом, сама схема тока не потребляет (разве что в те мгновения, когда происходит процесс ее переключения — но это, в среднем, доли микроватта). ТТЛ-вариант схемы логического элемента И-НЕ дан на рис. 5, в. Из рассмотрения рисунка вполне очевидно, что схема представляет собой стандартный элемент И (рис. 2.5, в), к которому добавлен выходной стандартный усилитель — от инвертора (см. рис. 2.7, б). Условные изображения логического элемента И-НЕ показана на рис. 2.9, г.

2.6 Логические элементы ИЛИ-НЕ

Изменив схему логического элемента ИЛИ на МОП-транзисторах возможно получить новый, более универсальный элемент ИЛИ-НЕ, осуществляющий одновременно с логическим сложением ИЛИ и логическое отрицание (инверсию) НЕ. Для этого активные элементы должны быть использованы не в режиме повторителей (как в схеме рис. 2.6, б), а в режиме усилителей-инверторов, что легко достигается перенесением общего сопротивления нагрузки из цепи истоков в цепь стоков. На рис. 2.10, а приведена такая схема логического элемента ИЛИ-НЕ. При сигналах логического 0 на входах А и В транзисторы VT2 и VT3 заперты, а поскольку транзистор VT1 постоянно открыт и играет роль сопротивления нагрузки, то на выходе Q действует положительное напряжение логической 1. Если на одном из входов А или В (или одновременно на двух) действует положительное, напряжение, соответствующее логической 1, то транзистор VT2 или VT3 или оба вместе оказываются открытыми и напряжение на выходе Q снижается до нескольких десятых долей-единиц вольт, т. е. до уровня напряжения логического 0.

Существенно снизить потребление энергии питания и увели чить быстродействие позволяет использование КМОП-транзисторов. В частности, на рис. 2.10, б приведена схема такого вида. Транзисторы VT1 и VT2 имеют р-каналы и открываются, если на их затворы подается напряжение логического 0 (так как на их затворы, соединенные с плюсом источника питания, подается отрицательное напряжение в отпирающей полярности). При этом транзисторы VT3 и VT4, имеющие n-каналы, оказываются запертыми и напряжение на выходе Q близко к напряжению источника питания, т. е. к напряжению логической 1.

Рис. 2.9. – Логический элемент И-НЕ, выполненный на МОП-транзисторах с га-каналами (а), многоэмиттерном биполярном транзисторе и дополнительном усилителе (б), комплементарных МОП-транзисторах (в) и условные графические обозначения элементов ИЛИ-НЕ и И-НЕ в электронных схемах (г)

Если хотя бы на одном из входов действует напряжение логической 1, то один из транзисторов VT1 или VT2 закрывается, а поскольку они соединены последовательно, схема отключается от источника питания и на вы ходе Q напряжение равно 0. В добавление к этому открывается один из транзисторов VT3 или VT4 (включенных параллельно) и выход соединяется с общим проводом через весьма малое сопротивление 100—300 Ом. Таким образом, элемент действует в полном соответствии с таблицей истинности ИЛИ-НЕ (табл. 5.). Следует отметить, что схема чрезвычайно экономична и потребляет ток только в очень краткие мгновения, во время переключения, когда одни транзисторы открываются, а другие еще не успели закрыться.

![]() Таблица 2.5 – Функциональная таблица (таблица истинности) ИЛИ-НЕ

Таблица 2.5 – Функциональная таблица (таблица истинности) ИЛИ-НЕ

|

А |

B |

Q |

|

0 |

0 |

1 |

|

1 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

1 |

0 |

ТТЛ-вариант конструктивного исполнения схемы ИЛИ-НЕ на биполярных транзисторах приведен на рис. 2.10, в. Из рассмотрения рисунка видно, что схема объединяет в себе двухвходовый элемент ИЛИ (рис. 2.6, а) и инвертор НЕ (см. рис. 2.7, б). Если на входах А и В действуют напряжения логических 0, то переходы база - эмиттер транзисторов VT1 и VT4 открыты и через них протекает ток, минуя переходы база - коллектор. Вследствие этого заперты суммирующие транзисторы VT2 и VT3. Поэтому на базу транзистора VT5 через резистор R4 подается напряжение питания, полностью его отпирающее, в результате чего на выход Q поступает положительное напряжение, соответствующее логической 1.

Транзистор VT6, включенный параллельно выходу Q, при этом заперт и тока не проводит, ибо на его базу не подается напряжение (с резистора R2). Если хотя бы на одном из входов А или В действует напряжение логической 1, один из суммирующих транзисторов VT2 или VT3 отпирается, напряжение в точке соединения их коллекторов резко падает, что приводит к запиранию транзистора VT5 и на вход перестает поступать положительное напряжение. При этом оказывается открытым транзистор VT6 шунтирующий своим малым сопротивлением выход, поскольку на его базу начинает подаваться напряжение, снимаемое с резистора R2, включенного в цепь эмиттеров суммирующих транзисторов VT2, VT3 (один из которых проводит ток). Таким образом, схема работает в полном соответствии с табл. 5. Условное изображения логического элемента ИЛИ-НЕ дана на рис. 2.9, г.

|

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем