Создание информационно-справочной подсистемы САПР конструкторско-технологического назначения. Дискретные элементы

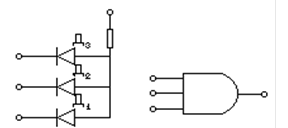

Операцию, осуществляемую блоком И, не следует смешивать с математической операцией сложения, так как выход блока И не есть сумма входных сигналов, как это следует из функциональной таблицы. Блок И широко используется в цифровых электрических схемах и обозначается символом, показанным на рис. 2.4,б.

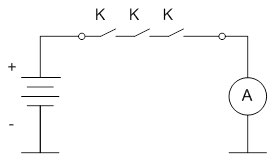

Рис.2.3. –

Цепочка последовательных ключей, схема И

а) б)

Рис.2.4 – а) диодная схема с тремя входами; ключей схемы логического И. б) ее символическое обозначение

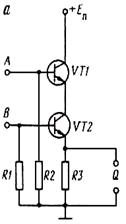

Схема простейшего двухвходового элемента И на биполярных транзисторах приведена на рис. 2.5, а, а на рис. 2.5, б – диаграмма его работы. Элемент И называют иногда схемой совпадения, так как из диаграммы работы видно, что сигнал 1 на выходе появляется только в том случае, на обоих входах А и В одновременно действуют напряжения логической 1. Поскольку транзисторы VT1 и VT2 соединены последовательно, то ток в цепи может протекать только в случае, если одновременно открыты оба транзистора. Если открыт только один из транзисторов, то ток протекать не будет и напряжение на выходе будет нулевым. Таким образом, схема выполняет логическое умножение И в соответствии с функциональной таблицей И.

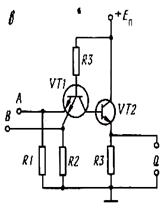

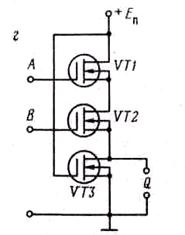

Схема логического элемента И в ТТЛ – варианте исполнения приведена на рис. 2.5, в. Особенность схемы – использование на входе многоэмиттерного транзистора VT1. Если на оба входа А и В поданы напряжения логического 0, то открыты оба перехода база -эмиттер транзистора VT1 и ток проходит только через них, не ответвляясь в переход база – коллектор. Вследствие этого транзистор VT2 закрыт и на выходе Q действует нулевое напряжение. Если на один из входов подается положительное напряжение логической 1, то соответствующий переход база – эмиттер транзистора VT1запирается. Однако основной переход база – коллектор не опирается, ибо конструкция многоэмиттерного транзистора (и режим работы) такова, что ток в цепи база – коллектор может протекать тогда, когда оказываются запертыми все переходы база – эмиттер. Таким образом, только при одновременной подаче на оба входа напряжения логической 1 отпирается переход база – коллектор транзистора VT1, что в свою очередь приводит к отпиранию транзистора VT2 появлению на выходе напряжения логической 1 в полном соответствии с правилом действия логического элемента И. МОП – вариант схемы логического элемента И приведен на рис. 2.5, г. Здесь, как и в предыдущих схемах, вместо сопротивления нагрузки используется МОП – транзистор с отпирающим напряжением на затворе.

а) б) в) г)

Рис.2.5. – Логический элемент И на биполярных транзисторах (а), диаграммы напряжений на его входах А, В я выходе Q (б); элемент И, выполненный на многоэмиттерном (б) и МОП-транзисторах (а)

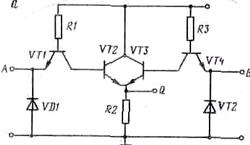

2.3 Логический элемент ИЛИ

Логическое утверждение «Если А или В истинно, тогда Q истинно» записывается так А+В=Q, где знак «+» есть символ, обозначающий операцию ИЛИ. Соответствующая этому определению Функциональная табл. 2.2. показывает, что выход получается при наличии любого входного сигнала. Принципиальная схема двухвходового логического элемента ИЛИ в ТТЛ- исполнении приведена на рис. 2.6, а. В соответствии с правилами логического сложения, если на входах А и В действуют сигналы логических 0, переходы база - эмиттер транзисторов VT1 и VT4 открыты и через них протекает ток. При этом, очевидно, через переходы база - кол лектор в транзисторах VT1 и VT4 ток не протекает, вследствие чего закрыты транзисторы VT2 и VT3 и на их общем сопротивлении в цепи эмиттеров R2 нет падения напряжения, т.е. выходной сигнал Q соответствует логическому 0. Если на одном из входов А или В действует сигнал положительной полярности, соответствующий логической 1, то происходят запирание перехода база — эмиттер транзистора VT1 (или VT4) и отпирание перехода база — коллектор. Это приводит к отпиранию транзистора VT2 (или VT3) и появлению на резисторе R2 - на выходе Q — почти полного напряжения источника питания (за вычетом падения напряжения в несколько десятых долей вольта на полностью открытом транзисторе VT2 или VT3). При подаче сигнала 1 на оба входа А и В открываются и оба выходных транзистора VT2 и VT3, что приводит к некоторому увеличению напряжения на выходе Q. Таким образом, рассмотренная электронная схема выполняет логическое сложение ИЛИ.

а) б)

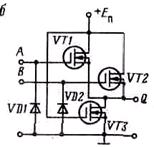

Рис. 2.6. – Логический элемент ИЛИ, выполненный на биполярных (а) и И МОП-транзисторах (б)

Таблица 2.2 – Функциональная таблица (таблица истинности) ИЛИ

|

А |

B |

Q |

|

0 |

0 |

0 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

1 |

1 |

Логический элемент ИЛИ на МОП-транзисторах может быть выполнен по схеме, приведенной на рис. 2.6, б. В этой схеме транзисторы VT1 и VT2 включаются при подаче на их затворы положительного напряжения логической 1 и выключаются, если действует напряжение логического 0. Транзистор VT3 используется вместо резистора и постоянно открыт, что приводит к потребле нию энергии питания, в то время когда открыты транзисторы VT1 и VT2.

2.4 Логический элемент НЕ

Это операция применяется в случаях, когда требуется иметь противоположные значения переменной. Противоположное значение переменной называется дополнением этой переменной Символически для НЕ оно обозначается чертой над соответствующей переменной величиной: А=Q.

Таблица 2.4 – Функциональная таблица (таблица истинности) НЕ

|

А |

Q |

|

0 |

1 |

|

1 |

0 |

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем