Счетчики и делители

Дешифраторы настроены на выделение неодинаковых состояний. Например, дешифратор на ЛЭ1 выделяет состояния 0, 2, 4 и т.д. через 2, на ЛЭ2 - 1, 5, 9 и т. д. через 4 на ЛЭ3 – 3, 11, 19 и т.д. через 8. Поэтому сигналы (импульсы) на выходах дешифраторов во времени не совпадают, и на общем выходе y получается их сумма.

Таким образом, за один цикл работы, который содержит 26 = 64 входных импульсов

, число импульсов на выходе y будет меньше и определяется числом

![]()

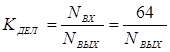

в соответствии с кодовой комбинацией на входах K0…K5. Коэффициент деления

.

.

Если только один из сигналов K’i = 1, то NВЫХ = 2i и коэффициент деления – целое число. В остальных случаях коэффициент деления – число дробное.

Следует обратить внимание на то, что если входная последовательность импульсов периодическая, то выходная последовательность будет периодической только тогда, когда коэффициент деления - целое число, в других случаях выходные импульсы распределены во времени неравномерно.

С целью увеличения диапазона перестройки коэффициента деления, микросхемы соединяют последовательно. Сигналы переноса играют роль входных по отношению к последующим микросхемам.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

- Проект городской телефонной станции на основе пакетной транспортной сети

- Система охранной сигнализации

- Электрические станции сети и системы

- Исследование преобразований частотного спектра в возмущенных условиях

- Анализ задачи общего воздействия динамическим магнитным полем на человека и формирование требований на технические средства комплексной магнитотерапии

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем