Разработка функциональной цифровой ячейки от функциональной логической схемы проектируемого узла до печатной платы узла

1. Задание на курсовую работу

Простановка номеров цепей в соответствие с техническим заданием

Первым этапом работы является простановка номеров цепей на принципиальной схеме в соответствие с техническим заданием. В нашем случае цепи представляют собой выводы, соединенные с общей шиной, которая, в свою очередь соединена с разъемом. Всего на схеме 18 элементов. В соответст

вие с техническим заданием они представляют собой 6 отдельных микросхем К155ЛА4 в корпусе DIP 14 по 3 «ЗИ-НЕ» (3 секции) с 4 выводами (3 входа и один инверсный выход). Поэтому был создан элемент: символ элемента в Symbol Editor, посадочное место и тип корпуса элемента (в Pattern Editor), затем символ и посадочное место были объединены в компонент и сохранены в библиотеке с помощью Library Executive [1, 2]. В редакторе Schematic работают с принципиальной схемой. Вместо компонента на шаблоне ставится созданный элемент. Используется Place Port. Стирают цепи и номера цепей, затем элемент соединяется проводом с шиной посредством Place Wire. Затем назначается номер новых цепей (Place Wire+ Port Properties/Net Name). Номера цепей, подходящих к разъему, назначаются произвольно (из списка номеров в техническом задании). Результатом является исходная функционально-логическая схема проектируемого узла (задание на курсовой проект).

2. Компоновки логических элементов в корпуса

Компоновка типовых элементов конструкции

Компоновка – первый этап конструкторского синтеза, при котором определяется однозначное соответствие между функционально-логическим, схемотехническим и конструкторским делением проектируемого устройства. Предполагается, что конструкция разбивается на унифицированные и неунифицированные элементы нескольких уровней конструкторской иерархии.

На этапе компоновки могут решаться задачи типизации, покрытия и разрезания.

Типизация – это процедура выделения в схеме частей, повторяющих друг друга, при этом число типов может быть задано, либо определяться в процессе типизации.

Покрытие – это определение минимального числа корпусов, покрывающих логические элементы принципиальной схемы, то есть задача покрытия решается на этапе перехода от логической схемы к электрической.

Разрезание – это разбиение общей схемы на части, число которых либо задано, либо определяется в процессе разрезания, при этом стремятся обеспечить минимум суммы межблочных связей.

В курсовой работе решается задача разрезания заданной схемы устройства на подсхемы с целью определения принадлежности логических элементов отдельным микросхемам.

Алгоритм разрезания схемы состоит из двух этапов:

– предварительное разрезание (быстрое получение результата)

– окончательная компоновка (улучшение результата итерационным методом).

Последовательный алгоритм предварительной компоновки:

1. Построение матрицы смежности взвешенного графа схемы А.

2. Для каждого элемента рассчитывается его суммарная тяга к остальным элементам.

3. Выбирается элемент, имеющий максимальную локальную степень.

4. Выбранный элемент помечается меткой т. Вначале выполнения алгоритма m=0.

5. Выбираются все элементы, связанные с выбранными ранее, но непомеченные метками.

6. Увеличивается метка m=m+l. Помечаются выбранные в блоке 5 элементы метками т.

7. Выполняются блоки 5, 6, 7 пока не будут помечены все элементы.

8. Выбирается очередной модуль верхнего уровня М j для компоновки.

9. Компонуются в Mj элементы с младшими метками, не вошедшие в компоновку ранее.

10. Компоновка в Mj заканчивается, когда модуль полностью заполнен.

11. Продолжается выполнение блоков 8–11, пока не будут заполнены все модули или пока не будет исчерпан список элементов.

12. Выход из алгоритма.

Итерационный алгоритм улучшения компоновки:

Процесс оптимизации выполняется путем последовательной перестановки элементов из разных модулей.

Пусть элемент Ej установлен в модуль Ms, а элемент Ej установлен в модуль Mt.

Рассчитываем показатель качества перестановки:

Rij = R внш it + R внш jt – R внт i – R внт j – 2 Rij, где

Rвнш it – количество связей Ei с элементами в Mt, Rbhui jt количество связей Ej с элементами в Ms, R внт i – количество связей Ei внутри модуля, R внт j – количество связей Ej внутри модуля. Выбираем ту пару, для которой показатель качества перестановки максимален.

Алгоритм:

1. Ввод начальной компоновки.

2. Расчет матриц связности Cs и Cst и заполнение их.

3. Расчет матрицы эффективности перестановок Rij для всех пар модулей.

4. Выбирается из этих матриц максимальный элемент.

5. Проверка: если показатель качества перестановок отрицательный, переход к блоку 7, иначе к блоку 6.

6. Перестановка элементов Ei и Ej и возврат к блоку 2.

7. Выход из алгоритма. Дальнейшее улучшение с помощью данного алгоритма невозможно [3].

Таким образом, 18 логических элементов размещаются в 6 микросхемах (по 3 элемента в каждой) оптимальным образом. Для этого используем программу PROG (18 элементов, 6 блоков максимальные значения входных данных для компоновки). Алгоритм работы в этой программе:

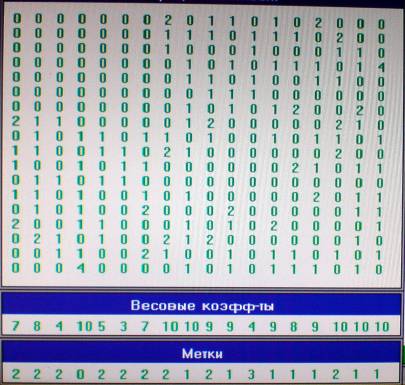

1) В соответствии со своей принципиальной электрической схемой заполняют симметричную матрицу смежности. В этой матрице у нас будет 18 строк и 18 столбцов, что соответствует количеству логических элементов. Последовательно перебирая все элементы, ищут номера повторяющихся цепей. На пересечении i-той строки и j-ro столбца ставят цифру (от 1 до 4), которая и означает количество связей, одинаковых цепей i-ro элемента с j-тым. Главная диагональ такой матрицы – нули. Заполнив матрицу, смотрят предварительную схему соединений (F2). В ней 64 внешних связей и 7 внутренних. Таким образом, на данном этапе используют последовательный алгоритм предварительной компоновки, предварительное разрезание (быстрое получение результата) в автоматическом режиме. Полученная матрица представлена ниже:

Таблица 1

Где весовой коэффициент – числовой коэффициент, параметр, отражающий значимость, относительную важность, «вес» данного фактора, показателя в сравнении с другими факторами, оказывающими влияние на изучаемый процесс.

Весовые коэффициенты равны количеству связей конкретного элемента с остальными элементами схемы.

Обозначение элементов метками:

1. Выбирается элемент с имеющий максимальную локальную степень (чей весовой коэффициент максимален) – элемент №4. Для данного элемента устанавливается метка М = 0.

2. Выбираются элементы, связанные с элементом с М = 0. Данные элементы помечаются меткой М = 1. Элементы №9, 11, 13, 14, 15, 17, 18

3. Выбираются элементы, связанные с элементами с М = 1 и не имеющими меток. Данные элементы помечаются меткой М = 2. Элементы 1, 2, 3, 5, 6, 7, 8, 10, 16.

4. Выбираются элементы, связанные с элементами с М = 2 и не имеющими меток. Данные элементы помечаются меткой М = 3. Элемент 12.

На этом этап обозначение элементов метками закончен. Далее идет первоначальная компоновка элементов.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем