Применение контроля информационных слов и их адресов по mod 3 в цифровых устройствах автоматики

![]() ,

, ![]() .

.

Алгоритм контроля состоит в сложении (вычитании) контрольных характеристик чисел А и В, а затем в сравнении суммы (разности) с суммой чисел ![]() по модулю q.

по модулю q.

Контрольное соотношение для операци

и умножения ![]() имеет вид:

имеет вид:

![]() .

.

Однако это соотношение справедливо, когда не происходит потери разрядов произведения при их выходе за пределы разрядной сетки. Если эту потерю учесть, то получим:

![]() ,

,

где ![]() — остаток от значения разрядов, отбрасываемых при округлении.

— остаток от значения разрядов, отбрасываемых при округлении.

Следовательно, для контроля операции умножения необходимо:

- произвести умножение по модулю q контрольных характеристик rа и rb;

- сформировать из отбрасываемых разрядов Е контрольную характеристику ![]() ;

;

- вычесть по модулю q из произведения ![]() величину

величину ![]() ;

;

- сравнить по модулю q полученный результат с величиной ![]() .

.

Для контроля операции деления ![]() используются соотношения:

используются соотношения:

![]() ;

; ![]() ,

,

где А — делимое; В — делитель; Z— частное; W — остаток от деления А на В, откуда следует контрольное соотношение:

![]() .

.

Следовательно, контроль операции деления состоит в следующем:

- получить от частного Z и остатка W контрольные характеристики rz и rw;

- произвести умножение rа и rb по модулю q;

- сложить полученное произведение по модулю q с rw;

- сравнить полученную сумму ![]() с контрольной характеристикой делимого rа .

с контрольной характеристикой делимого rа .

В зависимости от количества разрядов, формы представления числа, способа выполнения основной операции над числами приведенные выше алгоритмы могут несколько видоизмениться, однако принципы их построения остаются неизменными.

Рассмотрим принципы построения алгоритма контроля следующих логических операций:

— поразрядного логического сложения C=A V B;

— поразрядного логического умножения С=A ^ B;

—поразрядного сложения по модулю 2 ![]() .

.

Используя соотношения:

![]() ,

, ![]() ,

,

после преобразований и перехода к остаткам, можно получить контрольные соотношения:

для операции поразрядного логического сложения

![]() ;

;

для операции поразрядного логического умножения

![]() ;

;

для операции поразрядного сложения по mod 2

![]() .

.

Здесь ![]() ,

, ![]() ,

, ![]() — контрольные характеристики результата операции логического сложения (V), логического умножения (^), сложения по модулю 2(

— контрольные характеристики результата операции логического сложения (V), логического умножения (^), сложения по модулю 2(![]() ) соответственно.

) соответственно.

Аналогичным образом получаются алгоритмы операций сдвига, инвертирования, пересылок и т. д.

Функциональные схемы контролирующих устройств

Функциональные схемы контролирующих устройств создаются на основе алгоритмов контроля операций.

Покажем, как строятся функциональные схемы устройств для контроля счетчика, множительного и делительного устройств.

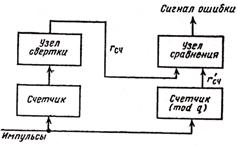

Схема контроля счетчика представлена на рис. 1.15. Она имеет в своем составе счетчик по модулю q, узел свертки и узел сравнения. В каждом такте (после поступления одного импульса) или периодически через несколько тактов содержимое основного счетчика сворачивается и величина rсч сравнивается с содержимым контрольного счетчика r’сч . Если ![]() , то вырабатывается сигнал ошибки.

, то вырабатывается сигнал ошибки.

Рис. 1.15

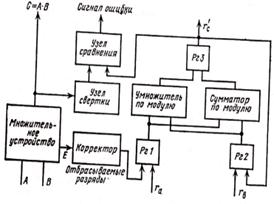

Схема для контроля множительного устройства представлена на рис. 1.16. Работа устройства заключается в следующем. Одновременно с поступлением чисел A и B на регистры Рг1 и Рг2 поступают контрольные характеристики ra и rb , которые перемножаются по модулю q, и величина rа * rb mod q пересылается с регистра Рг3 на регистрРг2.

Рис. 1.16

По мере выполнения операции умножения в основном множительном устройстве младшие отбрасываемые цифры произведения через корректор записываются в разряды регистра Pг1. Корректор служит для инвертирования отбрасываемых цифр произведения, а также распределения их в соответствии с весами по разрядам регистра Pгl. Инвертирование позволяет вместо операции вычитания rЕ при получении величины r'с выполнить операцию сложения с величиной ![]() . Распределение же отбрасываемых цифр по разрядам Pгl нужно для того, чтобы каждая цифра попала в тот разряд регистра Pгl, который соответствует ее весу. Каждый раз после того, как разряды Pгl будут полностью заполнены, его содержимое суммируется по модулю с записанной на регистре Рг2 величиной rа * rb mod q. Полученная величина через регистр Рг3 вновь записывается на регистр Рг2.

. Распределение же отбрасываемых цифр по разрядам Pгl нужно для того, чтобы каждая цифра попала в тот разряд регистра Pгl, который соответствует ее весу. Каждый раз после того, как разряды Pгl будут полностью заполнены, его содержимое суммируется по модулю с записанной на регистре Рг2 величиной rа * rb mod q. Полученная величина через регистр Рг3 вновь записывается на регистр Рг2.

Так по мере выхода отбрасываемых разрядов произведения за пределы разрядной сетки множительного устройства происходит постепенная корректировка величины r'с . После завершения операции умножения на регистре Рг3 будет записана скорректированная величина r'с.

Произведение С=А*В сворачивается и сравнивается с величиной r'с. При их несовпадении выдается сигнал ошибки.

Вариант схемы устройства для контроля работы делительного устройства представлен на рис. 1.17. Работа устройства происходит в следующем порядке. Одновременно с поступлением чисел A и B в делительное устройство на регистры Рг2 и Рг4 поступают их контрольные характеристики ra и rb . После выполнения операции деления частное Z и остаток W последовательно одно за другим сворачиваются и их контрольные характеристики записываются на регистры Рг3 и Рг1 соответственно. Затем с помощью умножителя и сумматора по модулю получают величину ![]() , которая поступает на регистр Рг5. После этого на схеме сравнения проверяется выполнение условия ra=r’a . Если условие не выполняется, то вырабатывается сигнал ошибки.

, которая поступает на регистр Рг5. После этого на схеме сравнения проверяется выполнение условия ra=r’a . Если условие не выполняется, то вырабатывается сигнал ошибки.

Другие рефераты на тему «Коммуникации, связь и радиоэлектроника»:

Поиск рефератов

Последние рефераты раздела

- Микроконтроллер системы управления

- Разработка алгоритмического и программного обеспечения стандарта IEEE 1500 для тестирования гибкой автоматизированной системы в пакете кристаллов

- Разработка базы данных для информатизации деятельности предприятия малого бизнеса Delphi 7.0

- Разработка детектора высокочастотного излучения

- Разработка микропроцессорного устройства для проверки и диагностики двигателя внутреннего сгорания автомобиля

- Разработка микшерного пульта

- Математические основы теории систем