Мехатронная система обеспечения заданной скорости электровоза на различных участках пути

§ удлиняют время исполнения прерывания A, что не соответствует его новому приоритету. Поэтому для понижения уровня приоритета текущего прерывания всегда следует закончить текущую задачу, и начать новую с более низким приоритетом. Это можно осуществить при установке бита IR в каком-либо незадействованном регистре управления xxIC.

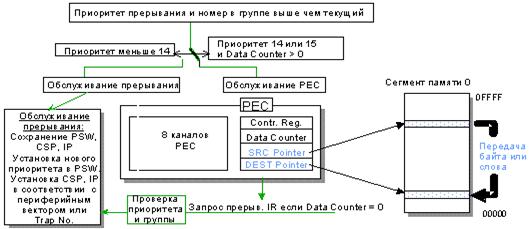

§ Контроллер периферийных событий - Peripheral Events Controll

er (PEC) освобождает ЦПУ от простых, но частых обслуживаний прерываний, осуществляя перенос данных в любую позицию нулевого сегмента без переключения задачи. Процесс переноса данных практически не затрагивает работу контроллера и не зависит от выполняемой программы - контроллер только приостанавливает выполнение текущей программы на один цикл (100 нс), даже не сохраняя свое состояние в стеке. Время отклика контроллера для обслуживания PEC составляет от 150 до 450 нс при цикле ЦПУ 100 нс. Для контроллера PEC отведены два верхних уровня приоритета, что позволяет обслуживать одновременно 8 каналов PEC. Каждый канал управляется собственным регистром PEC, который позволяет программировать передачу байта или слова данных с инкрементом адреса или без него с однократным, многократным или бесконечным числом пересылок. Обработка прерываний PEC выполняется в соответствии с приведенной диаграммой ( рисунок 3.5).

Рисунок 3.5 – Диаграмма прерываний

3.5 Генерация системного такта

§ Временной дискретой для ядра C166 является период такта, равный 50 нс при тактовой частоте 20 МГц. Большая часть команд C166 исполняются за два такта, т.е. за 100 нс. Для достижения номинального быстродействия внутренний такт должен иметь скважность 50%, что не всегда может быть получено при тактировании от кварцевого резонатора. При несовпадении длительностей высокого и низкого уровня тактового сигнала временная дискрета определяется по длительности самого короткого уровня, который должен быть не меньше 50 нс. Это означает, что при асимметрии такта понижается максимально возможная тактовая частота. Например, при длительности высокого уровня 50 нс, а низкого - 60 нс рабочая частота равна 18 МГц. Кроме требования симметричности времена переключения уровней тактового сигнала должны быть не более 5 нс.

§ Поэтому для генерации полностью симметричного системного такта в состав некоторых микроконтроллеров семейства C166 входит встроенный делитель входной частоты на 2. В этом случае требуется кварцевый генератор, работающий на частоте 40 МГц. Члены семейства, имеющие в маркировке индекс 'W' не содержат делителя и тактируются непосредственно. Без делителя сегодня выпускаются только кристаллы 8xC166W, с которыми рекомендуется работать на тактовой частоте 18 МГц.

§ В новых кристаллах C163, C164CI, C167 присутствует встроенное устройство PLL, которое преобразует входную частоту во внутренний системный такт с коэффициентом умножения 0.5, 1, 1.5, 2, 2.5, 3, 4 и 5. Например, при использовании кварцевого генератора 5 МГц для достижения обычных 20 МГц на встроенном устройстве PLL осуществляется умножение входной частоты на 4. Задание режима PLL осуществляется на фазе сброса при подключении резистора между входом P0L и нулем. При потере внешнего такта генерируется

§ прерывание, и PLL продолжает работать на частоте 5 .10 МГц. Внутренний такт отслеживается PLL также в режимах прямого тактирования и деления входной частоты на 2.

|

P0H.7 |

P0H.6 |

P0H.5 |

Коэффиц. умножения |

Фактор PLL |

Делитель |

Комментарий |

|

1 |

1 |

1 |

4 |

4 |

OFF |

по умолчанию |

|

1 |

0 |

1 |

2 |

2 |

OFF | |

|

1 |

1 |

0 |

3 |

3 |

OFF | |

|

1 |

0 |

0 |

5 |

5 |

OFF | |

|

0 |

1 |

1 |

W |

OFF |

OFF |

прямой такт |

|

0 |

0 |

1 |

0.5 |

OFF |

ON |

через делитель |

|

0 |

1 |

0 |

1.5 |

3 |

ON | |

|

0 |

0 |

0 |

2.5 |

5 |

ON |

3.6 Периферия микроконтроллера 80С166

3.6.1 Блоки таймеров общего назначения (GPT1 & GPT2)

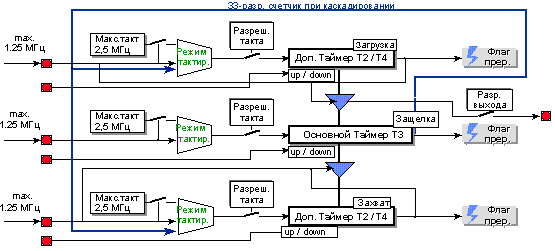

Микроконтроллеры семейства С166 могут содержать один или два модуля таймеров общего назначения с внешними входами / выходами, функциями перезагрузки и сравнения и возможностью объединения. Один из модулей (GPT1) имеет три 16-ти разрядных реверсивных таймера. Таймер T3 работает как основной, а таймеры T2 и T4 как дополнительные. Регистр дополнительного таймера может служить для перезагрузки основного таймера при его переполнении или для захвата содержимого основного таймера при возникновении внешнего события. Имеется также возможность каскадного соединения основного и одного из дополнительных таймеров для увеличения разрядности (рисунок 3.6). При этом образуется 33-х разрядный таймер (в цепочку включается еще и триггер на выходе таймера T3). Каждый из таймеров имеет собственный регистр управления. На блок-схеме GPT1 все временные значения приведены для частоты 20МГц.

Рисунок 3.6 – Блок схема 33-разрядного счетчика

Таймеры могут работать в следующих основных режимах:

§ счетчик внешних входных импульсов с максимальной частотой до 1,25 МГц;

§ таймер с внешним сигналом управления (активный высокий или низкий уровень);

§ таймер с входным тактом от внутреннего тактового генератора, который проходит через делитель с программируемым коэфф. от 8 до 1024.

В таблице приведены значения входной частоты и периода таймера при частоте тактового генератора 20 МГц.

|

Предварит.делитель |

8 |

16 |

32 |

64 |

128 |

256 |

512 |

1024 |

|

Вх. частота |

2.5 МГц |

1.25 МГц |

625 кГц |

312.5 кГц |

156.25 кГц |

78.125 кГц |

39.06 кГц |

19.53 кГц |

|

Миним. шаг |

400 нс |

800 нс |

1.6 мкс |

3.2 мкс |

6.4 мкс |

12.8 мкс |

25.6 мкс |

51.2 мкс |

|

Период |

26 мс |

52.5 мс |

105 мс |

210 мс |

420 мс |

840 мс |

1.68 с |

3.36 с |

Другие рефераты на тему «Транспорт»:

Поиск рефератов

Последние рефераты раздела

- Проект пассажирского вагонного депо с разработкой контрольного пункта автосцепки

- Проектирование автомобильных дорог

- Проектирование автотранспортного предприятия МАЗ

- Производственно-техническая база предприятий автомобильного транспорта

- Расчет подъемного механизма самосвала

- Системы автоблокировки

- Совершенствование организации движения и снижение аварийности общественного транспорта в городе Витебск