Аппаратное и программное обеспечение простых микропроцессорных систем

Программная реализация временной задержки использует метод программных циклов, при котором в какой-либо регистр блока регистров общего назначения (РОН) микропроцессора загружается число, которое при каждом проходе цикла уменьшается на единицу. Так продолжается до тех пор, содержимое регистра-счетчика не станет равным нулю, что интерпретируется программой как момент выхода из цикла. Время задерж

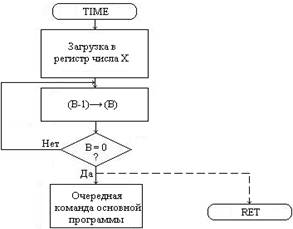

ки при этом определяется числом, загруженным в регистр-счетчик, и временем выполнения команд, образующих цикл. Схема алгоритма такой программы показана на рис. 6.

Рис. 6. Блок-схема временной задержки

Программа имеет символическое название «TIME» и, в случае вызова её основной программой по команде CALL, адрес TIME, должна завершаться командой возврата RET.

Предположим, что в МП-системе, использующей тактовую частоту 2 МГц (такт в этом случае составляет 0,5 мкс), необходимо реализовать временную задержку длительностью 250 мкс. Фрагмент программ, реализующей временную задержку, необходимо оформлять в виде подпрограммы, так как предполагается, что основная программа будет обращаться к ней многократно.

Текст программы, отображающей структуру алгоритма, показанного на рис. 6, следующий:

TIME: MVI B, X; загрузка регистра В числом Х

COUNT: DCR B; уменьшение на 1 содержимого

регистра В JNZ, адрес COUNT; повторить цикл, если В≠0

RET; возврат в основную программу, если В=0.

Для получения требуемой временной задержки необходимо определить значение числа Х, загружаемого в регистр В. Определение числа Х выполняется на основе времени выполнения команд, образующих данную подпрограмму. При этом необходимо учитывать, что команды MVI B, X и RET выполняются однократно, а число повторений команд DCR B и JNZ, адрес COUNT равно числу Х, загружаемому в регистр В. Кроме того, обращение к подпрограмме временной задержки осуществляется по команде CALL, адрес TIME, время исполнения которой также необходимо учитывать при подсчете временной задержки. В описании команд МП КР580ИК80 указывается, за сколько тактов основной частоты синхронизации исполняется каждая команда МП. На основе этих данных можно записать:

CALL, TIME – 17 тактов – 8,5 мкс;

MVI B, X – 7 тактов – 3,5 мкс;

DCR B – 5 тактов – 2,5 мкс;

JNZ, адрес COUNT – 10 тактов – 5,0 мкс;

RET – 10 тактов – 5,0 мкс.

Таким образом, однократно исполняемые команды (CALL, MVI, RET) в этой подпрограмме требуют 17 мкс (8,5+3,5+5,0). Следовательно, для получения требуемой задержки в 250 мкс необходимо команды DCR B и JNZ, COUNT столько раз, чтобы время их исполнения составило 233 мкс, т.е. (250–17). Однако время выполнения этой пары команд составляет (2,5+5,0). Поэтому, если принять Х=31, возможно получение временной задержки 232,5 мкс.

Если точность подпрограммной реализации временной задержки длительностью 250 мкс с погрешностью – 0,5 мкс удовлетворяет условиям задачи, то на этом разработка программы заканчивается.

Исходя из приведенного расчета, запишем текст подпрограммы TIME:

TIME: MVI B, 31 ; загрузка в регистр В числа 31

COUNT: DCR B; декремент регистра В

JNZ, адрес COUNT; цикл, если В≠0

RET; возврат в основную программу.

В том случае, если точность представления временного интервала 250 мкс с погрешностью – 0,5 мкс не удовлетворяет разработчика, можно поступить двояко:

– реализовать подпрограмму точной задержки на 50 мкс и пятикратно повторить ее вызов;

– путем внесения в подпрограмму пустых операций NOP и соответствующего изменения набора команд (с целью устранения временного рассогласования 0,5 мкс) обеспечить точную временную выдержку.

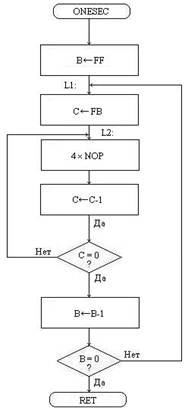

Во многих случаях применения МП-систем требуется сформировать длительные временные задержки (секунды, минуты, часы и т.д.). Сделать это при частоте, равной 2МГц с использованием ранее описанного метода невозможно, так как максимальной емкости регистровой пары FFFF не хватит для того, чтобы представить число Х, достаточное для формирования задержки в 1 секунду. Сформировать столь большую для МП задержку можно с использованием метода вложенных циклов (как показано на рис. 7).

С целью получения задержки, равной 1 мин, основная управляющая программа может 60 раз осуществлять вызов подпрограммы ONESEC. Для этого число 60 загружается, например, в регистр В, который выполняет функции декрементного счетчика секунд, и после каждого прогона подпрограммы ONESEC его содержимое уменьшается на 1. Текст программы «ONESEC» приводится ниже.

ONESEC: MVI B, FF; счетчик внешних циклов

L1: MVI C, FB; счетчик внутренних циклов

L2: NOP; точная подгонка времени

внутреннего цикла

NOP;

NOP; время

NOP;

DCR C; декремент счетчика внутренних циклов

JNZ, адрес L2; возврат во внутренний цикл, если С≠0

DCR В; декремент счетчика внешних циклов

JNZ, адрес L1; возврат во внешний цикл, если В≠0

RET

Рис. 7. Алгоритм задержки на 1 секунду

Блок-схема типовой процедуры сбора и формирования в ОЗУ МП-системы массива данных от одного источника показана на рис. 8. Источником вводимых данных является порт ввода с символическим адресом NN, 8100 – начальный адрес массива данных, регистр С используется в качестве счетчика данных и регистровая пара HL используется командами с косвенно-регистровой адресацией в качестве указателя данных; ETX – знак-терминатор «конец массива».

Рис. 8. Типовая процедура сбора данных

Программа имеет вид:

LXI H, 8100; запись начального адреса

8100 → (H+L)

MVI C, C, 00; счетчик = 0

SAVE: IN, NN; ввод данных из порта в А

MOV M, A; перенос данных А → ячейку ОЗУ,

адрес которой в (H+L)

INX H; (H+L) = (H+L+1)

INR C; счетчик = счетчик+1

SUI, ETX; проверка терминатора

JNZ, адрес SAVE; продолжение сбора, если не 0

DONE

Если число слов данных известно и хранится в ячейке с адресом 81N0, то программа сбора данных будет иметь вид:

LXI H, 8100;

LDA, 81N0; пересылка содержимого 81N0 → (A)

MOV C, A; счетчик = длина массива: А → (С)

SAVE: IN, NN;

MOV M, A;

INX H;

DCR C; счетчик = счетчик-1

JNZ, адрес SAVE; продолжение сбора, если не 0

DONE

Рассмотрим несколько примеров обработки массива данных.

LDA COUNT; загрузка содержимого М 8200

(COUNT) → (A)

MOV B, A; загрузка счетчика: (В) ← (А)

LXI H, 8100; запоминание в (H+L) адреса начала

массива данных

SUB A; сброс аккумулятора: (А) ← 0

ADDN: ADD M ; прибавление элемента М+(А) → (A)

INX H; переход к следующему адресу

(H+L) ← (H+L+1)

DCR B; декремент счетчика: (В) ← (В-1)

JNZ, адрес ADDN; организация цикла, если не 0

DONE

LDA COUNT; загрузка содержимого

М (COUNT) → (A)

MOV B, A; организация счета в регистре В:

Другие рефераты на тему «Программирование, компьютеры и кибернетика»:

Поиск рефератов

Последние рефераты раздела

- Основные этапы объектно-ориентированного проектирования

- Основные структуры языка Java

- Основные принципы разработки графического пользовательского интерфейса

- Основы дискретной математики

- Программное обеспечение системы принятия решений адаптивного робота

- Программное обеспечение

- Проблемы сохранности информации в процессе предпринимательской деятельности