Общие сведения о счетчиках

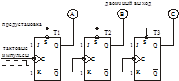

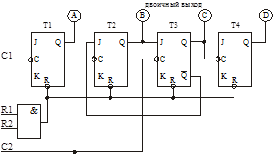

Рис.13.4. Схема синхронного счетчика по модулю 8

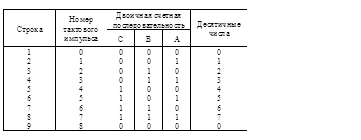

Последовательность двоичных чисел, проходимая счетчиком за один цикл счета (счетная последовательность) приведена в табл.13.2.

Таблица 13.2.

Счетная последовательность импульсов

Рассмотрим принцип работы данного счетчика в течение одного цикла счета. На каждом

шаге цикла входной импульс поступает на синхронизирующий вход каждого триггера.

Импульс 1 — строка 2 табл.13.2. Переключается только триггер T1, поскольку только у него на входах J и K действует уровень логической 1. T1 переходит из состояния 0 в состояние 1.

Результат: на выходе счетчика 001.

Импульс 2 — строка 3. Переключаются два триггера T1 и T2, поскольку на входах J и K этих триггеров действует уровень логической 1. T1 переходит из состояния 1 в состояние 0, T2 — из состояния 0 в состояние 1.

Результат: на выходе 010.

Импульс 3 — строка 4. Переключается только один триггер. T1 переходит из состояния 0 в состояние 1. T2 не переключается, поскольку на входах J и K действует уровень логического 0.

Результат: на выходе 011.

Импульс 4 — строка 5. Все триггеры меняют свое состояние на противоположное. T1 и T2 переходят из 1 в 0. T3 переключается из 0 в 1.

Результат: на выходе 100.

Импульс 5 — строка 6. Триггер T1 переходит из состояния 0 в состояние 1.

Результат: на выходе 101.

Импульс 6 — строка 7. Переключаются два триггера. T1 переходит из 1 в 0, T2 - из 0 в 1.

Результат: на выходе 110.

Импульс 7 — строка 8. Триггер T1 переходит из состояния 0 в состояние 1.

Результат: на выходе 111.

Импульс 8 — строка 9. Все триггеры меняют свое состояние, переходя из 1 в 0.

Результат: на выходе 000.

Следует заметить, что в данном счетчике JK‑триггеры используются как в режиме переключения (J=K=1), так и в режиме блокировки (J=K=0).

Вычитающие счетчики

Помимо суммирующих счетчиков (прямого счета), рассмотренных выше, существуют счетчики которые считают в обратном направлении - вычитающие.

Рассмотрим схему асинхронного вычитающего счетчика по модулю 8 (рис.13.5).

Рис.13.5. Схема асинхронного вычитающего счетчика по модулю 1

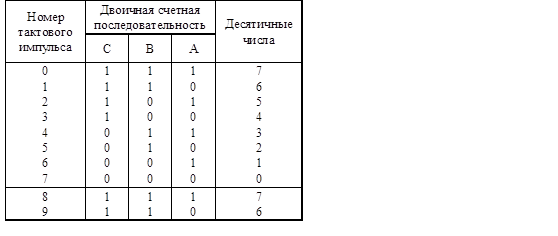

Отличие данной схемы от схемы суммирующего счетчика (рис.13.1) состоит в способе переноса сигнала от триггера к триггеру. В суммирующем счетчике синхронизирующий вход каждого триггера связан с прямым выходом Q предыдущего триггера. В вычитающем счетчике синхронизирующий вход каждого триггера связан с инверсным выходом ![]() предыдущего триггера. В счетчике изображенном на рис.13.5, перед началом счета в обратном направлении предусмотрена предварительная его установка в состояние 111 (десятичное число 7) с помощью входа предустановки (S). Счетная последовательность двоичных чисел приведена в табл.13.3.

предыдущего триггера. В счетчике изображенном на рис.13.5, перед началом счета в обратном направлении предусмотрена предварительная его установка в состояние 111 (десятичное число 7) с помощью входа предустановки (S). Счетная последовательность двоичных чисел приведена в табл.13.3.

Таблица 13.3.

Счетная последовательность импульсов

Самоостанавливающиеся счетчики

Вычитающий счетчик, схема которого показана на рис.13.5 — счетчик циклического типа. Когда этот счетчик приходит в состояние 000, он снова начинает счет с двоичного числа 111. В некоторых случаях нужны счетчики, которые останавливаются, когда исчерпывается вся счетная последовательность. Рассмотрим, какие изменения нужно внести в схему вычитающего счетчика, чтобы счет прекращался при достижении состояния 000.

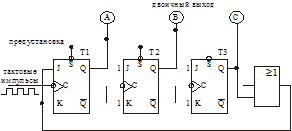

Рис.13.6. Схема самоостанавливающегося счетчика

Из рис.13.6 видно, что для этого нужно ввести в схему логический элемент ИЛИ, который будет устанавливать на входах J и K триггера T1 уровень логического 0, когда на выходах (C, B, A) счетчика появится сигнал 000. Если нужно начать новый цикл счета с двоичного числа 111, на вход предустановки S следует подать уровень логического 0.

Используя один логический элемент или их комбинацию, можно останавливать счет прямом и обратном направлении, на любом наперед заданном двоичном числе. Выход логического элемента нужно для этого присоединить к входам J и K первого триггера в асинхронном счетчике. При этом триггер T1 переводится в режим хранения.

Счетчики — делители частоты

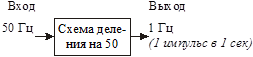

Одной из функций которую выполняют счетчики в цифровых системах, является деление частоты. Пример простой системы с делителем частоты показан на рис.13.7. Эта система составляет основу цифровых часов. Периодический сигнал электросети с частотой 50 Гц, сформированный в виде последовательности прямоугольных импульсов, подается на вход системы, которая делит частоту на 50.

Рис.13.7. Система с делителем частоты

На выходе схемы имеем последовательность прямоугольных импульсов с частотой 1 Гц (1 импульс в 1 сек). Это таймер секунд.

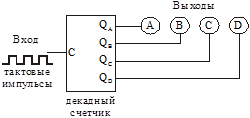

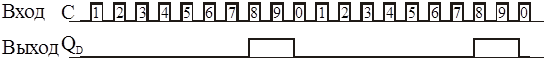

На рис.13.8 схематически изображен декадный счетчик, а на рис.13.9 приведены временные диаграммы для его синхронизирующего входа C и выхода QD, соответствующего двоичному разряду восьмерок.

Рис.13.8. Схема декадного счетчика

Рис.13.9. Временные диаграммы декадного счетчика

Из рис.13.9 видно, что 20 импульсов на входе счетчика преобразуются в 2 выходных импульса. Выполняется деление 20/2=10. Снимая сигнал с входа QD, декадного счетчика, получим счетчик‑делитель на 10. Т.е. частота выходного сигнала состовляет 1/10 частоты на входе счетчика.

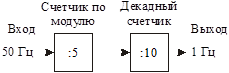

Последовательно соединяя рассмотренный декадный счетчик (счетчик‑делитель на 10) и по модулю 5 (счетчик‑делитель на 5) получим схему, осуществляющую деления частоты на 50. Структура такой схемы показана на рис.13.10. Последовательность прямоугольных импульсов с частотой 50 Гц поступает на вход счетчика - делителя на 5, а с его выхода с частотой 10 Гц подается на вход счетчика‑делителя на 10. На выходе схемы получим сигнал с частотой 1 Гц.

Рис.13.10. Структурная схема делителя частоты на 50

Функция деления частоты используется в таких цифровых устройствах, как частотомер, осциллограф и т.п.

Интегральные схемы счетчиков

На рис.13.11 представлена схема четырехразрядного двоичного счетчика‑делителя на 2, на 6 и на 12 (К155ИЕ4).

Рис.13.11. Схема четырехразрядного двоичного счетчика

Если подать тактовые импульсы с частотой f на вход С1, то на выходе А получим частоту f/2. Тактовые импульсы с частотой f на входе С2 запускают делитель на 6 и на выходе D имеем частоту f/6. При этом на выходах B и C имеем импульсы с частотой f/3. На выводы R1 и R2 подаются команды сброса. Для построения счетчика с модулем деления 12, требуется соединить делители на 1 и на 6, соединив выход А со входом С2. На вход С1 подается входная частота f, на выходе D получаем последовательность импульсов с частотой f/12.

Другие рефераты на тему «Программирование, компьютеры и кибернетика»:

Поиск рефератов

Последние рефераты раздела

- Основные этапы объектно-ориентированного проектирования

- Основные структуры языка Java

- Основные принципы разработки графического пользовательского интерфейса

- Основы дискретной математики

- Программное обеспечение системы принятия решений адаптивного робота

- Программное обеспечение

- Проблемы сохранности информации в процессе предпринимательской деятельности